IC Station

IC Station

Dette dokumentet beskriver:

- DRC (Design rule check)

- LVS (Layout versus schematic test)

- Ekstrahering av parameter fra utlegg

Online dokumentasjon kan leses fra firefox på mikroserver2 /prog/mentor/2006.2b_rhelx86linux/icflow_home/shared/htmldocs/_bk_icpl/_bk_icpl.html.

Vi antar nå at IC studio er startet, se IC studio. I tillegg er skjemaet ferdig laget og det er laget et Viewpoint.

Create cell

Når vi skal lage et utlegg i IC station begynner vi med å lage et nytt "View". Klikk på det biblioteket ditt og høyre-klikk deretter i Cell-vinduet og velg "New View". Velg "View Type" layout og trykk deretter Next og velg "Block" under Layout Definition og vpt_c35b4 under Connectivity Source. Deretter trykker du Finish. Du skal nå få opp IC station.

DRC (Design Rule Check)

DRC sjekker at utlegget er korrekt i henhold til de design rules som gjelder for prosessen. DRC sjekker ikke om transistorer er riktig koblet sammen. Det gjøres i LVS-testen som beskrives senere.

- Fra paletten: Velg ICrules, deretter Check.

- Velg Options i pop-up vinduet.

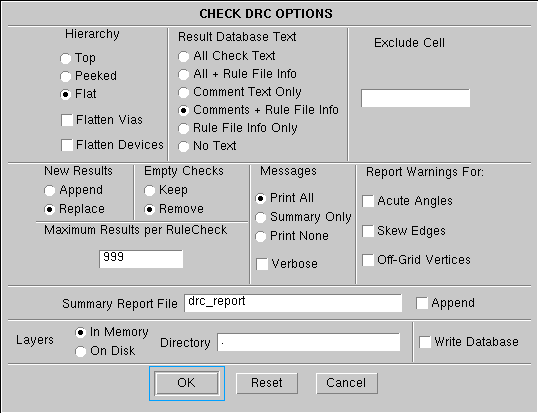

- Set Maximum results per rule check til et passende tall, og velg andre instillinger, f.eks. slik som vist under.

- Klikk OK

- Klikk OK i pop-up vinduet for å kjøre DRC.

- Bruk så knappene First og Next for å se på feil for feil.

- Feilene markeres med en hvit ramme i utlegget samtidig som det står en forklarende melding nederst på skjermen.

DRC kan også startes fra menyen øverst i vinduet. Se bilde.

LVS (Layout Versus Schematic test)

Når utlegget har passert DRC må vi kjøre LVS-sjekk. Her sjekkes at utlegget stemmer overens med skjemaet. LVS kontrollerer at skjema og utlegg er samme elektriske krets. Dersom noen komponenter er koblet feil sammen eller har feil størrelse i henhold til skjema, får vi melding om det.

OBS! Hvis du har åpnet et "logic" i forbindelse med SDL, må dette lukkes nå. Velg File --> Logic --> Close.

- Fra paletten: Velg ICtrace(M)

- Fra menylinjen velg HIT-KIT Utilities > Setup LVS (ICtrace)

- Klikk på Mask Mode

- Fra paletten: Klikk på Load Rules

- Velg SDL og klikk OK

- Fra paletten: Klikk på LVS

- Trykk på knappen Setup LVS...

- Trykk på knappen Setup Trace Props

- likk OK begge steder for å kjøre LVS.

Sjekk rapportfilen. Hvis LVS-testen gikk bra vil du se et smilefjes i rapporten.

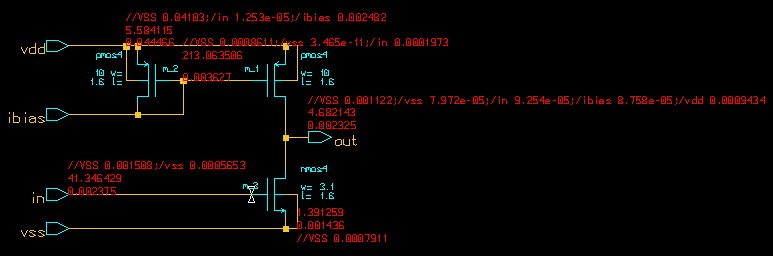

Når LVS-testen er vellykket kan vi åpne et vindu i IC Station som viser skjemaet. Velg Logic --> Open, og angi stien til viewpointet (samme som Source Name i dialogboksen LVS (Mask)). Ved å klikke på et nett eller en transistor, vil tilsvarende markeres i utlegget.

IC-extract (Ekstrahering av parasitter)

Når vi simulerer skjemaet vårt i DA simulerer vi bare skjema. Dvs. transistormodeller med ideelle ledninger mellom. Simulatoren vil ikke ta hensyn til parasittiske kapasistanser og resistanser i utlegget. Slike parasitter er avhengig av hvordan transistorene er tegnet, hvor tett vi plasserer dem, hvordan vi foretar ruting osv. For å finne ut hvordan kretsen på utlegget egentlig virker må vi ekstrahere disse parasittene, importere dem i skjemaet vårt og kjøre simulering en gang til. Parasitter representerer ekstra poler, som kan føre til at systemet ikke lengre tilfredsstiller spesifikasjonene. Derfor er det viktig å simulere skjemaet med effektene fra utlegget.

Lag en kopi av det originale skjemaet du tegnet i DA (Save sheet as...). Lukk det "gamle" og åpne det nye. Lag et viewpoint av det nye skjemaet. Vi skal bruke det nye skjemaet til simulering med informasjon fra utlegget.

Er du i simuleringsmodus? Gå ut av simuleringsmodus.

I IC Sation:

- Fra paletten: Velg ICextract (M)

- Lukk eventuelle åpne logic.

- Klikk Lumped og fyll ut dialogboksen tilsvarende figuren under.

- Åpne skjemaet i DA igjen og gå i simuleringsmodus.

- Legg til transistormodellene som skal brukes i simuleringen.

- Klikk Lib/Temp/Inc og legg til følgende sti (for S35):

$AMS_DIR/eldo/s35/cmos53tm.mod

- Fra paletten, velg Annotations --> Merge all

- Informasjonen fra utlegget er nå inkludert, og fargen har skiftet fra rød til gul.

- Sett opp simulering (analyser, plot) og kjør.

Simulering med parasitteffekter som egen nettliste

AustriMicroSystems beskriver i filen /prog/design_kits/ams_hk_3.70/www/hitkit/hk370/icstation/icextract.html en metode for å lage en selvstendig nettliste for krets med parasittiske effekter ekstrahert fra layout. Denne simuleres så i DA-IC ved å slå av generering av netlist (Session->Environment->Run Sim) og så kjøre simulering hver gang man har ekstrahert på ny.

Et viktig tips er å kjøre ekstrahering fra pull-down menyene Extract->Mask-Lumped eller Extract->Mask->Distributed istedenfor å velge tilsvarende fra paletten. Dermed får man satt de riktige default verdier, og scriptet rewrite_netlist kalles automatisk for nødvendig konvertering av bl.a. modellnavn og måleenheter.

Nettlisten som kommer ut inneholder kretsen i en subscircuit. Ved å kommentere vekk linjene med .subckt og .ends kan nettlisten kopieres over nettlisten generert av DA-IC og simuleres med samme plot og målinger. Alternativt kan man i DA-IC velge den ekstraherte nettlisten i Setup->Session->Environment.