FreeRTOS FSBL

Tested on Xilinx Vivado/SDK 2017.3, Ubuntu 16.04 LTS.

This tutorial assumes you have completed the "Running FreeRTOS on Xilinx Zybo"-tutorial.

Creating FSBL

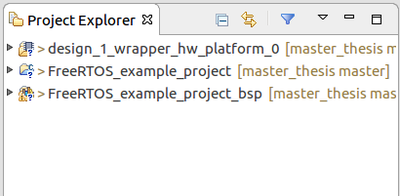

The result from the previous tutorial linked at the top of this tutorial, should be a Project Explorer looking like this:

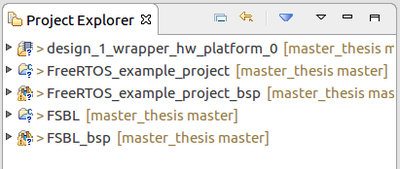

Goto File --> New --> Application Project. Name the new project "FSBL" and let OS platform be "standalone". On the next page, choose the "Zynq FSBL"-template. Finish. The Project Explorer should now contain the following:

Goto Xilinx --> Create Boot Image. Choose the Zynq architecture and click to browse for a Output BIF file path. Name the file "output.bif" and create a folder called "output" within the axi4_lite_tutorial_project.sdk directory. Click OK. Check that the output format is "BIN". Now click add in the Boot Image Partitions section:

Choose "Bootloader" as partition type, and navigate to the file "FSBL.elf" under \axi4_lite_tutorial_project.sdk\FSBL\Debug\ in the file path.

Now add a new partition, this time as type "datafile". The file that should be added to file path is "design_1_wrapper.bit" under \axi4_lite_tutorial_project.runs\impl_1\

The third and final partition is of type "datafile", has the name "FreeRTOS_example_project.elf", and is found at \axi4_lite_tutorial_project.sdk\FreeRTOS_example_project\Debug\

When all partitions have been added, click "Create Image". Navigate to the directory you specified for output, in our case \axi4_lite_tutorial_project.sdk\output.

It should now contain two files: BOOT.bin, and output.bif. Copy the BOOT.bin file onto an SD-card formatted as FAT.

Bring up your favorite Xilinx Zybo SoC board, and configure jumper 5 (JP5) for SD boot configuration. Insert the SD card, and connect a power source (wall or USB). Then power up the board. After a couple of seconds, it should behave just as it did when booting from JTAG in the "Running FreeRTOS on Xilinx Zybo"-tutorial.