Creating example project with AXI4 Lite peripheral in Xilinx Vivado

Tested on Xilinx Vivado 2017.3, using the Xilinx Digilent Zybo SoC.

Start ./vivado from installed directory.

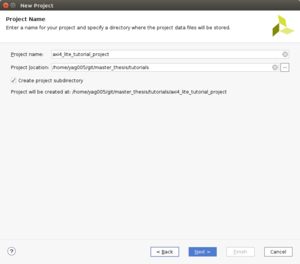

Goto: File -> New Project -> Next. For this project we will name it "axi4_lite_tutorial_project" and place it in a folder named tutorials. Click Next and choose RTL Project, then Next.

Do not add any sources, but make sure that both target and simulator language is set to the appropriate language you're using. In this project we will use VHDL. Click Next. Here you must provide a constraints file named "ZYBO_Master.xdc", available from GitHub. Make sure that the option to copy the constraints file(s) into the project is marked.

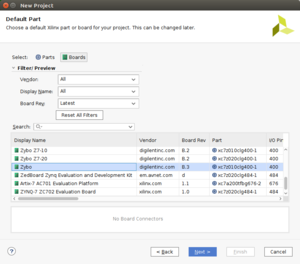

For the next step, the board files for the board we're using must have been installed. If this is not the case, follow this tutorial to do so.

Choose the Zybo board, click next, and finish.

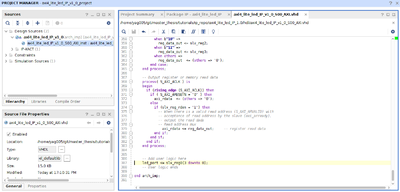

The project has now been created and ready for IP-block integration.

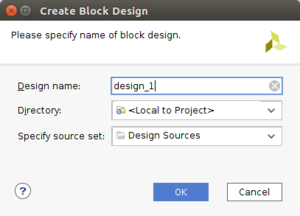

Click on "Create Block Design" in the left of the window. Give the design a name, for instance design_1, and click "OK".

Now press the "+" button in the diagram window, and search for "ZYNQ7 Processing System". Double click to add. In the top of the window an option to "Run Block Automation" appears.. Click this, and complete with default settings. The window should now look like this:

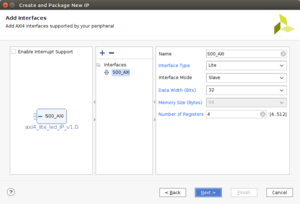

Goto: Tools -> Create and Package New IP. Choose "Create a New AXI4 peripheral", and click next. Name the IP "axi4_lite_led_IP" or any other suiting name. You can leave all other parameters default.

In the next window, ensure the IP contains one slave interface named S00_AXI of type "Lite". Click next, and choose "Add IP to the repository". Finish.

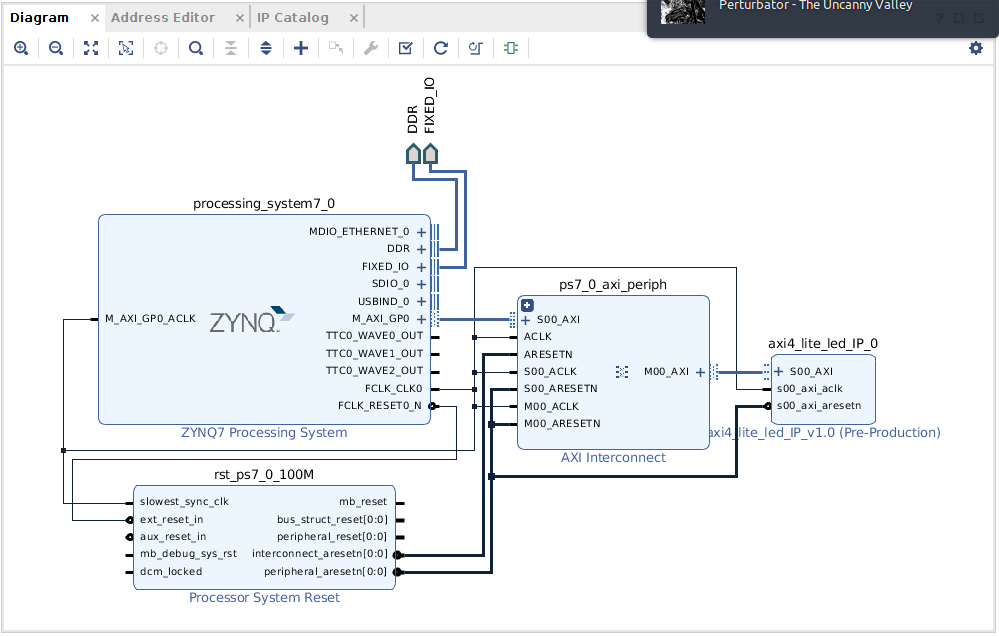

In the diagram window it's now possible to add the IP we just created, using the "+" button. Search for "axi4_lite_led_IP_v1.0" and add it. Run connection/block automation with default parameters.

Right click on "design_1" under "Block Designs" in the Sources design tree. Click "Create HDL Wrapper", and let Vivado manage wrapper and auto-update.

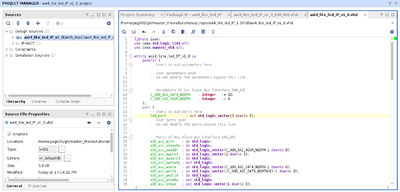

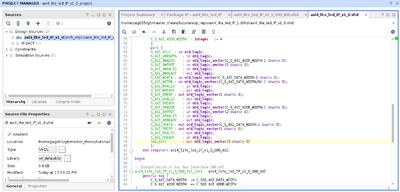

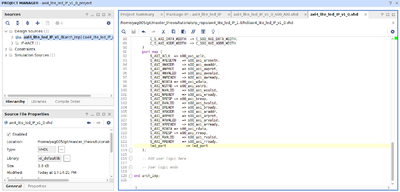

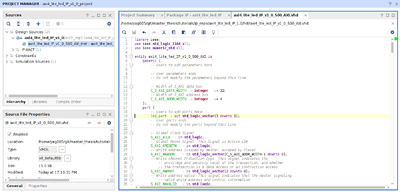

Right click axi4_lite_led_IP_0 block --> Edit in IP Packager. Then do the following edits to axi4_lite_led_IP_v1_0_S00_AXI.vhd and axi4_lite_led_IP_v1_0.vhd

Save both files, and go into the "Ports and interfaces" tab. Click "Merge changes from Ports and Interfaces Wizard". A new port should now be listed named "led_port". Click on "Review and Package", and click Re-Package IP. Click yes on prompt to close project.

Click on "IP Status" tab, and choose "Upgrade Selected" if you are not automatically prompted. Go back to the Block design diagram, and right-click on the newly created port named "led_port[3:0]" on our custom IP and choose "make external". Save.

Open the constraints file ZYBO_Master.xdc located under Constraints in the sources tab design tree.

To avoid tons of warnings, comment out everything except from the 4 lines under "##LEDs".

Rewrite them to the following:

set_property -dict { PACKAGE_PIN M14 IOSTANDARD LVCMOS33 } [get_ports { led_port[3] }];

set_property -dict { PACKAGE_PIN M15 IOSTANDARD LVCMOS33 } [get_ports { led_port[2] }];

set_property -dict { PACKAGE_PIN G14 IOSTANDARD LVCMOS33 } [get_ports { led_port[1] }];

set_property -dict { PACKAGE_PIN D18 IOSTANDARD LVCMOS33 } [get_ports { led_port[0] }];

Save the file, and click "Generate Bitstream". Accept the launch of synthesis and implementation.

When complete, you can choose to open the implemented design and have a look at it, or specify timing restraints.

Exporting Bitstream

Goto: File --> Export --> Export Hardware, and choose to include bitstream.

You are now done with this tutorial.