Simulering av VHDL: Difference between revisions

| Line 13: | Line 13: | ||

==Starte Questa Sim== | ==Starte Questa Sim== | ||

Når man skal arbeide med Questa Sim fra Mentor Graphics skriv følgende kommando i et terminalvindu. | Når man skal arbeide med Questa Sim fra Mentor Graphics skriv følgende kommando i et terminalvindu. | ||

Generelt ligger programvaren i /eda/Siemens, og versjonene ligger i mapper sortert på årstall. | |||

ssh -X mikroserver4 | ssh -X mikroserver4 | ||

export LM_LICENSE_FILE=1717@lisensserver | export LM_LICENSE_FILE=1717@lisensserver | ||

source /eda/ | source /eda/Siemens/2023-24/scripts/QUESTA-CORE-PRIME_2023.4_RHELx86.sh | ||

vsim | vsim | ||

Revision as of 07:54, 24 January 2024

Konstruksjon og simulering av VHDL-kode med Modelsim/Questa

Innledning

Hensikten med denne oppgaven er å få et lite innblikk i bruk av høynivåspråk for simulering og uttesting av kretsløsninger. I denne oppgaven skal vi bruker VHDL (Very high speed integrated circuit Hardware Description Language), som er spesielt utviklet for elektronikk. VHDL er definert slik at det passer i en mengde sammenhenger, og er det vil derfor være uoverkommelig å gå inn på detaljer i denne oppgaven. Vi skal ta for oss noen eksempler:

- Eksempel 1: Signalflyt i en SR-lås

- Eksempel 2: Signaler og variable

Et VHDL program består i hovedsak av ENTITY, som definerer tilkobling mellom programmet og omverden, og ARCHITECTURE, som definerer programmets funksjon. Den komplette VHDL-koden for eksempel 1 vist nederst på denne siden.Mentor Graphics har utviklet programvare (Modelsim//Questa) som gjør det mulig å beskrivem, simulere og feilsøke VHDL-kode. Fremgangsmåten for skriving, kompilering og simulering av VHDL-kode finner du under.

Starte Questa Sim

Når man skal arbeide med Questa Sim fra Mentor Graphics skriv følgende kommando i et terminalvindu. Generelt ligger programvaren i /eda/Siemens, og versjonene ligger i mapper sortert på årstall.

ssh -X mikroserver4 export LM_LICENSE_FILE=1717@lisensserver source /eda/Siemens/2023-24/scripts/QUESTA-CORE-PRIME_2023.4_RHELx86.sh vsim

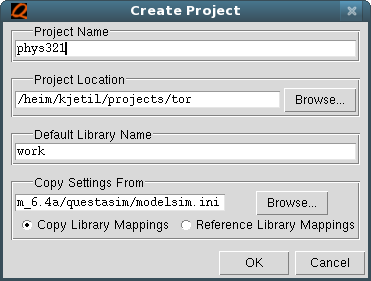

Lage et nytt prosjekt

I den følgende teksten er det vist hvordan man kan utføre kompilering, etc. på kommandolinjen. Dette kan enten gjøres i fra X terminalvinduet, eller fra kommandolinjen i Questa. Hvis man velger å bruke Questa-miljøet er de fleste prosedyrer/kommandoer tilgjengelige under menyen.

Start et nytt prosjekt med

File > New > Project

Velg et fornuftig navn og katalog. Man kan gjerne ha flere uavhengige vhdl-filer i et prosjekt. Det er en fordel å ha en hovedkatalog til vhdl prosjektene og en underkatalog for prosjektet fex /home/bruker/vhdl_prosjekt/sr_latch

Skriving av VHDL kode

En ny VHDL kode (et design beskrevet med VHDL kode) påbegynnes med å starte emacs i terminal vinduet eller ved å bruke den innebygde teksteditoren i Questa ved å velge Create New File.

Det fine med emacs er at man kan velge VHDL-modus. Dette gjøres med å skrive M-x vhdl-mode (M står for Meta og er vanligvis definert som esc-knappen). I emacs har en menyer med alle valg oppe langs kanten som i andre teksteditorer, men programmet skiller seg litt ut med kommandolinjen nederst i vinduet. Når en f. eks. skal lagre filen en har skrevet blir denne kommandolinjen aktiv og en skriver inn sti og filnavn der. Når man lagrer er ikke navnet på kodefilen viktig, men det er fornuftig å kalle den det samme som ENTITY-delen, med .vhdl som "etternavn" (f. eks. sr_latch.vhdl).

Kompilering av VHDL kode

Koden kompileres med

vcom sr_latch.vhdl

Hvis det er feil i koden vil det komme en melding i kommando vinduet. Dobbeltklikker du på feilen vil du få opp en liste over kompileringsprosessen og alle feilene. Dobbeltklikker du så på linjen som angir en feil så vises den respektive linjen i editoren.

Merk at navnet til det kompilerte designet blir skrevet med små bokstaver, selv om du har brukt store bokstaver i ENTITY- eller ARCHITECTURE-navnet. Det kompilerte designet blir liggende i work-katalogen.

Simulering og debugging i Questa

Når koden kompilerer feilfritt kan den simuleres i Questa. Dette startes med:

vsim

Nå dukker det opp en rute der du skal velge hva som skal simuleres, utvid work og velg vhdl filen. Eventuellt kan du skrive vsim work.sr_latch i kommandovinduet

Questa bruker et standard X-basert vindusoppsett, og er derfor noen forskjellig fra de andre Mentor-programmene. Når du starter simulatoren åpnes det et vindu som vist i figur 1. Begynn med å åpne diverse vinduer:

- View > Wave

- View > Objects

- View > Locals

Man kan også gi kommandoer i Questa-vinduet. F.eks.

Wave *

Dra de signalene du vil se på i wave vinduet fra object vinduet.

Signalverdier settes med kommandoen 'force' eller med

Force > Force (i "Signals" vinduet)

Dersom et av signalene skal være klokkesignal, kan dette gjøres enkelt med

Force > Clock (i "Signals" vinduet)

Eksempler

Signalflyt i en SR-lås

Simuler SR-låsen. Begynn med å påtrykke stimuli til alle signaler ved tid 0 (t0). Bruk STEP-knappen for å simulere på delta-tid-nivå. (Om en holder musepekeren over knappene i Questa, kommer det en forklarende tekst opp.) Når verdiene er stabile kjører du i f.eks. 100 ns før du endrer stimuli (skriv run 100 i et av vinduene). Tilsvarende kan du endre stimuli ved å skrive f.eks. force S 0 i hoved-vinduet. Legg merke til den røde pilen som peker på den linjen som blir utført.

Hvis du vil begynne på ny kan du velge

File > Restart -f

LIBRARY ieee; USE ieee.std_logic_1164.ALL; ENTITY SR_latch IS PORT ( S,R : IN std_logic ; Q,QB : INOUT std_logic ); END SR_latch; ------------------------------------------------------------------------------- ARCHITECTURE behave OF SR_latch IS BEGIN -- behave Q <= S nand QB; QB <= R nand Q; END behave;

Signaler og variable

Simuler VHDL-koden under. Bruk Step eller Step Over for å følge prosedyrens utvikling linje for linje. Simulere med optimaliseringsopsjon "-voptargs=+acc" for å kunne se variablene i wave-vinduet:

vsim -voptargs=+acc sign_var

Bruk View > Objects for å kikke på signalene og View > Local for å se innholdet i variablene. Forklar endringene i signaler og variable. Hva er forskjellen som funksjon av tid/delta-tid?

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

ENTITY sign_var IS

PORT (clk : IN std_logic);

END sign_var;

-------------------------------------------------------------------------------

ARCHITECTURE difference OF sign_var IS

signal SA: bit := '0';

signal SB: bit := '1';

begin -- difference

p_test: process

variable A: bit := '0';

variable B: bit := '1';

begin

wait until rising_edge(clk);

A := B;

B := A;

SA <= SB after 5 ns;

SB <= SA after 5 ns;

end process p_test;

end architecture difference;