SmartFusion2- AMBA APB, Custom Peripheral: Difference between revisions

No edit summary |

No edit summary |

||

| Line 31: | Line 31: | ||

[[File:Chip_osc.jpg|500 px]][[File:CCC_core.jpg|400 px]]<br> | [[File:Chip_osc.jpg|500 px]][[File:CCC_core.jpg|400 px]]<br> | ||

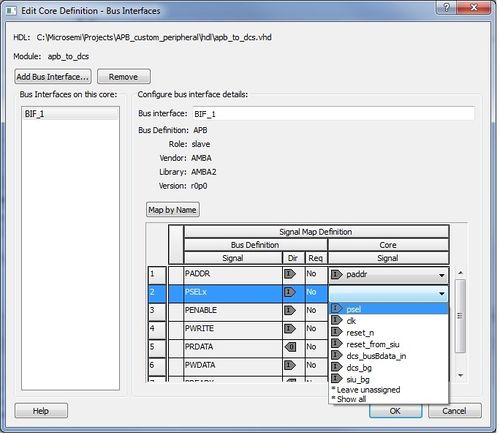

Now | Now import the vhdl files [[Media:APB_DCS_files.zip]] by clicking ''File'', ''Import'', ''HDL Source Files''. These files can now be found under ''hdl'' in the ''Files'' tab and in ''Design Hierarchy''. In ''Design Hierarchy'' right click on ''DCS_test'', choose ''Create Core from HDL''. Answer ''No'' to question about adding bus interfaces to core. Right click on ''apb_to_dcs'' and choose ''Create Core from HDL''. Choose ''Yes'' on question about adding bus interfaces to core. Choose ''Add/Edit bus interfaces...''. In next window, click ''Add Bus Interface...'', choose ''APB, AMBA, AMBA2, slave''. Connect ''PSELx'' to ''psel''.<br> [[File:Module_bus_interface.jpg|500 px]] | ||

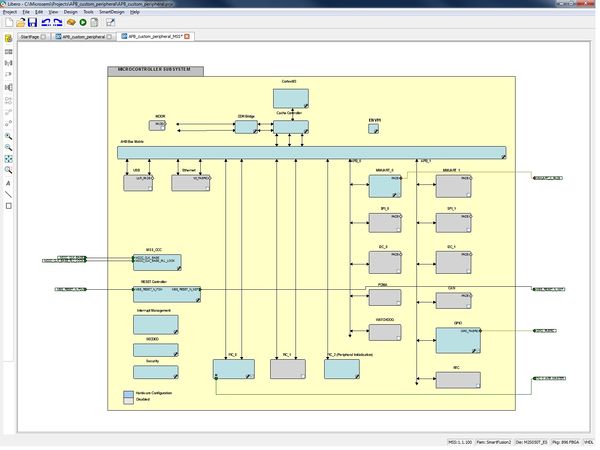

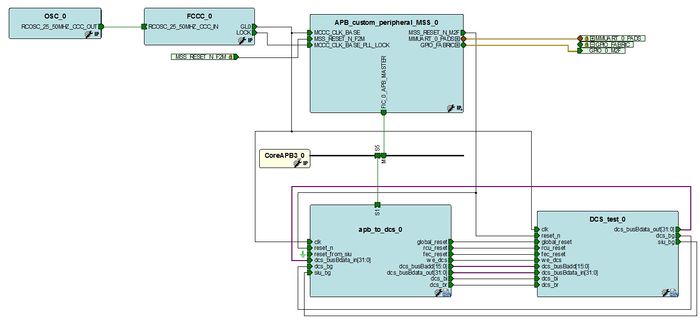

Add the modules you made to the SmartDesign. In design canvas, right click and choose ''Auto Connect'' followed by ''Auto Arrange Instances''. Right click on ''MSS_RESET_N_F2M'' and ''GPIO_FABRIC'' and select ''Promote to Top Level''. Right click on ''reset_from_siu'' and choose ''Tie Low''. Connect the unconnected wires. The result should look something like the image below [[File:SmartDesign_finished.jpg|700 px]] | Add the modules you made to the SmartDesign. In design canvas, right click and choose ''Auto Connect'' followed by ''Auto Arrange Instances''. Right click on ''MSS_RESET_N_F2M'' and ''GPIO_FABRIC'' and select ''Promote to Top Level''. Right click on ''reset_from_siu'' and choose ''Tie Low''. Connect the unconnected wires. The result should look something like the image below [[File:SmartDesign_finished.jpg|700 px]] | ||

| Line 39: | Line 39: | ||

=Pre-synthesized Simulation= | =Pre-synthesized Simulation= | ||

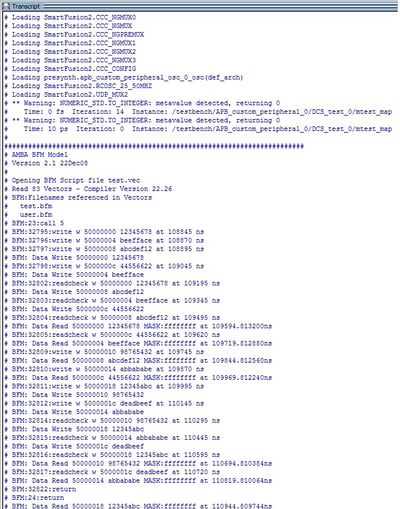

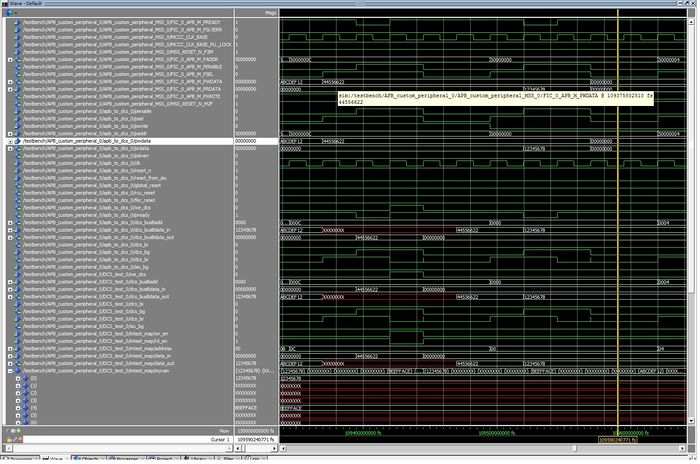

To simulate the functionality of the abp_to_dcs module, normal APB bus functionality from the MSS should be used. To do this | To simulate the functionality of the abp_to_dcs module, normal APB bus functionality from the MSS should be used. To do this you can add a .bfm file (Bus Functional Model). In the supplied files there is a file called User.bfm. Copy the content of this file to the User.bfm in your project, located under ''Files'' and ''simulation''. | ||

Next, go to ''Project'' and then ''Project Settings''. Choose ''DO File'' under ''Simulation Options''. You can use the run.do file supplied in the .zip. If you want to use automatic .do file and add signals yourself you can use standard settings, but be sure to change simulation time to 150 us. The system has got some initialization time, which takes around 120 us with this setup, before the bus signals start to change. | Next, go to ''Project'' and then ''Project Settings''. Choose ''DO File'' under ''Simulation Options''. You can use the run.do file supplied in the .zip. If you want to use automatic .do file and add signals yourself you can use standard settings, but be sure to change simulation time to 150 us. The system has got some initialization time, which takes around 120 us with this setup, before the bus signals start to change. | ||

Revision as of 09:42, 28 September 2013

Intro

This tutorial explains how to implement and test a custom AMBA APB (Advanced Peripheral Bus) module. The tutorial will create a SmartFusion2 MSS (Microcontroller Subsystem) with APB bus interface. The custom module will be connected to the APB bus to map from APB bus to a DCS bus. Connected to the DCS part there will be a test module, which you can write and read from. The MSS will also have a GPIO module connected to a LED and serial UART peripheral.

Before you start

Make sure you have installed Libero and have a valid license, as described in SmartFusion2. This tutorial assumes Libero v11.1 is used and that you are using the SmartFusion2 starter kit from Microsemi.

Create new project

Start Libero SoC v11.1. Press Project and New Project. Name your project APB_custom_peripheral. Use system tools SmartFusion2 Microcontroller Subsystem (MSS).

Modify MSS

Double click on the MSS component to modify it. A new window will open. Enable/Disable peripherals until your MSS looks like the image below.

Tip: click View > Maximize Work Area or CTRL+W to expand the working area while enabling and disabling the MSS peripherals.

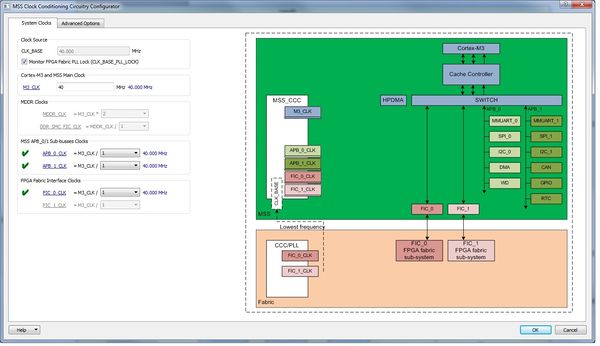

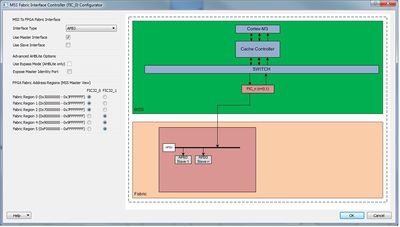

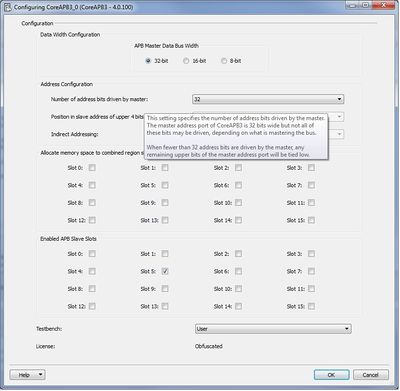

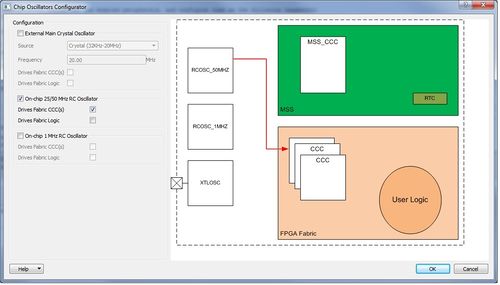

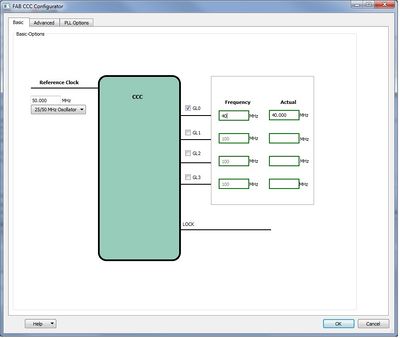

Click on the configuration button for the enabled peripherals, and configure them like the following images

MSS CCC

Reset Controller

FIC 0

MMUART 0

Your MSS should now look like this:

SmartDesign

Close the MSS configuration window. On the SmartDesign canvas, right click on the MSS component and Update instance(s) with Latest Component.

From Catalog add the following components:

CoreAPB3 from Bus Interfaces,

Chip Oscillators and Clock Conditioning Circuitry from Clock & Management

Now import the vhdl files Media:APB_DCS_files.zip by clicking File, Import, HDL Source Files. These files can now be found under hdl in the Files tab and in Design Hierarchy. In Design Hierarchy right click on DCS_test, choose Create Core from HDL. Answer No to question about adding bus interfaces to core. Right click on apb_to_dcs and choose Create Core from HDL. Choose Yes on question about adding bus interfaces to core. Choose Add/Edit bus interfaces.... In next window, click Add Bus Interface..., choose APB, AMBA, AMBA2, slave. Connect PSELx to psel.

Add the modules you made to the SmartDesign. In design canvas, right click and choose Auto Connect followed by Auto Arrange Instances. Right click on MSS_RESET_N_F2M and GPIO_FABRIC and select Promote to Top Level. Right click on reset_from_siu and choose Tie Low. Connect the unconnected wires. The result should look something like the image below

Generate component by clicking SmartDesign and Generate Component.

Pre-synthesized Simulation

To simulate the functionality of the abp_to_dcs module, normal APB bus functionality from the MSS should be used. To do this you can add a .bfm file (Bus Functional Model). In the supplied files there is a file called User.bfm. Copy the content of this file to the User.bfm in your project, located under Files and simulation.

Next, go to Project and then Project Settings. Choose DO File under Simulation Options. You can use the run.do file supplied in the .zip. If you want to use automatic .do file and add signals yourself you can use standard settings, but be sure to change simulation time to 150 us. The system has got some initialization time, which takes around 120 us with this setup, before the bus signals start to change.

Double click on Simulate in Design Flow under Verify Pre-Synthesized Design which will start ModelSim.

Constraints, Synthesize and Place&Route

Go to Project, Project Settings, Device I/O Settings and set Default I/O Technology to LVCMOS 3.3V.

Import the Physical Design Constraint file, Fabric_top.io, by clicking File, Import, I/O Constraints (PDC) Files. Once this is included, scroll in Design Flow to Place and Route and right click. Select Configure Options and uncheck Timing Driven.

Now you can click on the "Play" button, Generate Programming Data. This process will take some time. If all succeeds, you should be able to program your FPGA. Program it by connecting power and FlashPro Programmer and click on Run Programming Action.

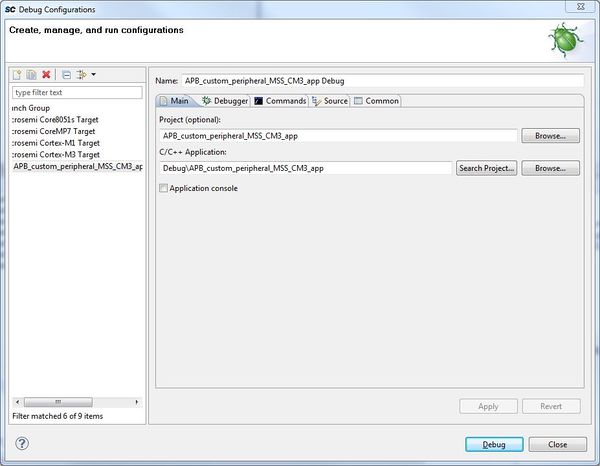

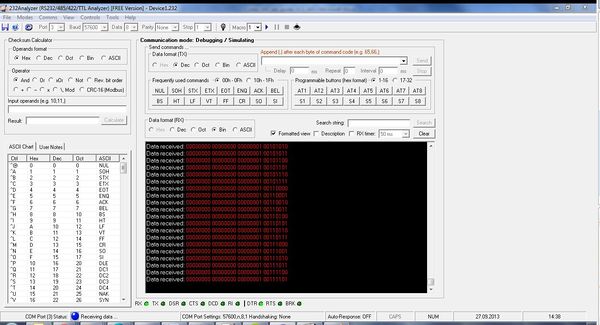

Create Test Software

To write test application software, scroll to the bottom of the Design Flow and click Write Application Code. This will open SoftConsole from Microsemi. You can replace the main.c with the main.c supplied in the .zip file. The application will then write data to RAM and then read it. A LED is linked to the LSB of the read data, which cause the LED to blink. Data read on first memory location is written to the UART, and can be observed with a serial terminal program. Note that serial data sent on the UART is counting binary, and ASCII format is not implemented. The UART also sends out a message on the UART if the read data is different from expected.

Build Debug Application by pressing Debug Configurations and then choose Microsemi Cortex M3 Target. Press Apply, build debug target and launch debug target.