Layout XL and IHP SG13S: Difference between revisions

mNo edit summary |

|||

| (2 intermediate revisions by 2 users not shown) | |||

| Line 1: | Line 1: | ||

= Before starting layout = | = Before starting layout = | ||

Read the Design Kit User Guide. | Read the Design Kit User Guide. It can be found on the SG13SFeatures tab on the Virtuoso console window, or in the folder "/eda/design_kits/ihp_sg13/SG13S_618_rev1.12.0/doc/pdf/" on the mikroserver. Especially the part of connecting the substrate (chapter 8.2) and layout (chapter 9). Also make sure you understand the Layout Rules document. | ||

Especially the part of connecting the substrate (chapter 8.2) and layout (chapter 9). Also make sure you understand the Layout Rules document. | |||

Other documents are found in "eda/design_kits/ihp_sg13/SG13S_618_rev1.12.0/doc/html/" | |||

If you're laying out just one cell (in our case a SRAM-cell) make sure it contains defined values and not just pPar("")-values. This makes it easier to produce the right transistor-sizes etc. If you do not want to change your schematic, make a copy to another cell (e.g. from "sram" to "sram-fixed"). | If you're laying out just one cell (in our case a SRAM-cell) make sure it contains defined values and not just pPar("")-values. This makes it easier to produce the right transistor-sizes etc. If you do not want to change your schematic, make a copy to another cell (e.g. from "sram" to "sram-fixed"). | ||

| Line 104: | Line 99: | ||

Then Launch -> ADE L to get the simulation setup. Setup -> Design and choose the config file from the test bench cell. Use the stimuli button to create the stimuli (copy the stimuli from the schematic simulation) for the test, and then run it. | Then Launch -> ADE L to get the simulation setup. Setup -> Design and choose the config file from the test bench cell. Use the stimuli button to create the stimuli (copy the stimuli from the schematic simulation) for the test, and then run it. | ||

If you want to simulate corners with the ptap1 and ntap1 components, you have to add two additional model files for your corner simulation. These model files for IHP 130nm process is located in /eda/design_kits/ihp_sg13/SG13S_618_rev1.12.0/tech/SG13_PASSIVES/spectre/ | |||

Add SG13_cornerCAP.scs and SG13_cornerRES.scs to your model files and click ok. Now you can add bcs(Best Case Scenario) and wcs (Worst Case Scenario) to each corner, remember to enable the "tick box" for each of them. When you are done, the corner setup should look something like this: | |||

[[File:Corner_setup.png|400px]] | |||

[[Category:Mikroelektronikk]] | [[Category:Mikroelektronikk]] | ||

Latest revision as of 14:29, 7 May 2021

Before starting layout

Read the Design Kit User Guide. It can be found on the SG13SFeatures tab on the Virtuoso console window, or in the folder "/eda/design_kits/ihp_sg13/SG13S_618_rev1.12.0/doc/pdf/" on the mikroserver. Especially the part of connecting the substrate (chapter 8.2) and layout (chapter 9). Also make sure you understand the Layout Rules document.

Other documents are found in "eda/design_kits/ihp_sg13/SG13S_618_rev1.12.0/doc/html/"

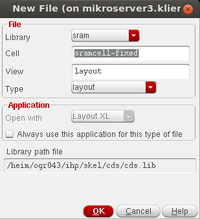

If you're laying out just one cell (in our case a SRAM-cell) make sure it contains defined values and not just pPar("")-values. This makes it easier to produce the right transistor-sizes etc. If you do not want to change your schematic, make a copy to another cell (e.g. from "sram" to "sram-fixed").

Layout XL

From the schematic click Launch -> Layout XL to open the layout environment.

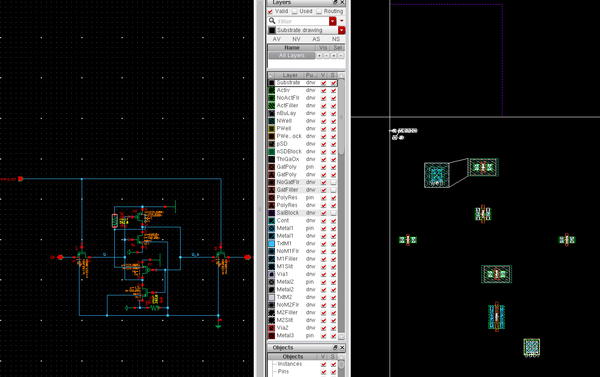

Layout XL opens with a new black empty canvas. The schematic window also opens. This is very useful as when we add our devices in the layout we can see which device they represent in the schematic as they get highlighted.

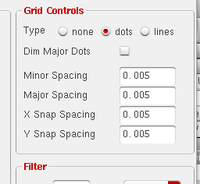

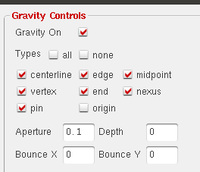

Before anything you must define some options to avoid a lot of DRC-errors down the line. In the Layout Rules-document we read what our drawing-grid restrictions are (bottom of page 10). In Layout XL press E to open the Display Options-window. Remember that all size-values are in micrometers. Set the X and Y Snap Spacing to reflect the grid rules. Now press Shift-E to open the Layout Editor Options. Set gravity on(you can turn this off later with the g-key if you dont like it), and aperture around 0.1. This defines the the distance before snapping to another object etc.

Generate from source

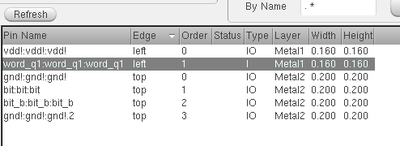

IHP has already defined transistors, pins, etc. for different sized, so it is not needed to draw these from scratch. You should, however, dissect them to understand how they work. To place all the devices from the schematic press Connectivity -> Generate -> All From Source. In this window we define which of our devices we want to place, the I/O pins, PR boundary (the area which our cell must be within) and floorplan settings (if needed). For our cell we need to change the IO-pins. We want the gnd and bit-lines to be vertical, and vdd and word-lines to be horizontal. This means that they will intersect each other and must be in different layers. We also want two gnd-pins which also can be defined here. Remember to uncheck Create under the sub!-pin since this is not needed.

Change the Label options to a smaller font size (about 0.1 is ok). Click OK to see the results.

The purple box is the PR boundary in which are layout must be contained. Notice how the ntap1 is highlighted in the schematic when clicked in the layout window.

Pin Placement

Press Place -> Pin Placement. This opens a windows that lets us define the position of our pins. This is very helpful to line up our design. Remember that the positions may be tweaked later.

Placing devices

If you are extremely lazy you can autoplace the components with Place -> Custom Digital -> Placer. This, however, will probably not give you the desired result. To help you place the the devices correctly it is helpful to see which devices that connect to each other and how. This is accomplished with Connectivity -> Nets -> Show/Hide All Incomplete Nets. This will give you a all the nets that are uncompleted and can be very daunting. However, you can use Ctrl++ (that is Ctrl and +-key ) to turn on or off the nets for the selected device.

F4 switches between Full and Partial Select. Partial Select means that we are able to select individual pieces of a device, e.g. if we want to stretch a part.

DRD

DRD stands for Dynamic Design Rule Checking and are helpful while laying out your design. DRD Enforce On prevents you from doing anything that breaks the rules, and DRD Notify tells you if what you are doing is illegal. Image below shows example of DRD Notify.

Drawing

To draw rectangles (e.g. NWell) choose the wanted layer on the left side then press R. To create a connection between to nodes you can either create a wire (Ctrl+W) or a path (P). A wire automatically helps with choosing layer, and may also be used to create vias to another layer by left-clicking.

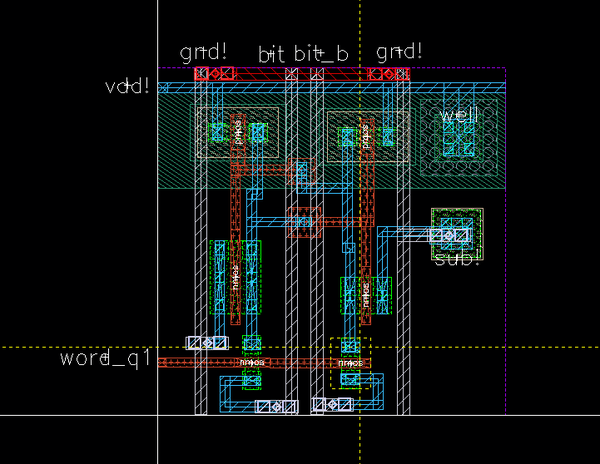

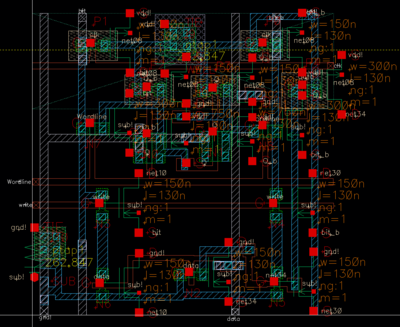

A complete layout could look something like this:

Note that there is a specified minimum enclosure in the design rules for vias between polysilicon and metal. This is because during the manufacturing process, the polysilicon and metal layers are created separately and the alignment is not perfect, so the polysilicon connection must be slightly larger to accommodate the potential offset between these layers. Enclosures can be seen by the polysilicon squares on the vias connecting the Q and Q_B lines in the design above. To set a via enclosure size, right click the via and go to properties. On the bottom, there is a setting for GatPoly enclosure. You must set each direction separately.

DRC

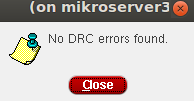

Run DRC by pressing Assura -> Run DRC. Make sure technology is SG13_dev and the Rule Set is default. Read about the different switches in the user guide (e.g. antenna-rules etc). If everything is ok this message should appear:

The DRC should also be run for Density. See IHP user guide for how to produce dummy metal to fill the design.

LVS

This is covered in chapter 12 of the user guide.

Run LVS by pressing Assura -> Run LVS. This will give you a match if the schematic and the layout match each other, or you will get some errors.

Parasitic extraction QRC

This is covered in chapter 14 of the user guide. Before you run the QRC, the LVS has to match.

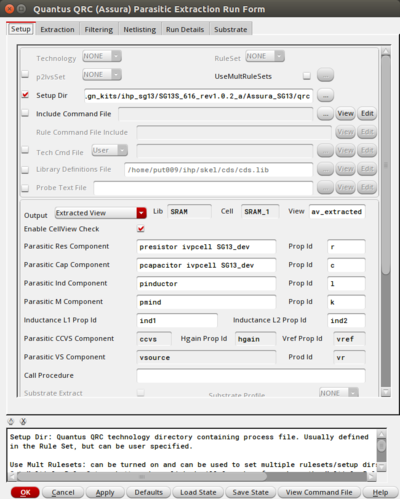

To do an extraction of your circuit click Assura -> Run Quantus. In "Setup Dir" make sure the path is set to "/eda/design_kits/ihp_sg13/SG13S_616_rev1.0.2_a/Assura_SG13/qrc", where the technology files for the qrc run is. Set the "Parasitic Res Component" to "presistor ivpcell SG13_dev" and the "Parasitic Cap Component" to "pcapacitor ivpcell SG13_dev". Open the Extraction tab and set your ground net (gnd!) in the "Reference node" box. Then run the QRC by pressing OK.

This should give you an extracted design called "av_extracted" in the cell of the library. This can be checked and viewed from the library manager. In this picture the extracted cell is a SRAM with bitline conditioning and a write driver.

Post layout simulation

In the library manager make an copy of the SRAM cell, to use as a test bench cell. Click file -> new -> Cell View and make an config file in your new test bench cell. Use "config" as the type, and click "ok". In the new window click on the "Use template" and select "AMS", and click "ok". Then edit the view list and add "av_extracted" with the add box. Clicking ok will then bring you to the hierarchy editor.

Then you need a test bench schematic. In your copied schematic you will have the whole SRAM or different symbols making up the SRAM, but for the simulation there should only be a symbol that matches the extracted layout. So go back to the schematic in the SRAM cell and make one symbol out of it. Put this symbol into the test bench schematic, and add the pins that are needed.

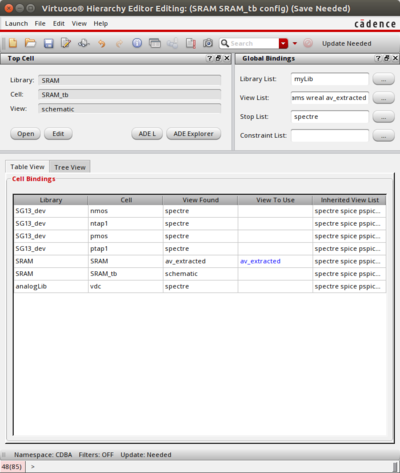

Go back to the hierarchy editor and change the View to your test bench schematic and update the hierarchy. Then right click on the "view found" for the SRAM from the SRAM cell, and select the av_extracted.

Then Launch -> ADE L to get the simulation setup. Setup -> Design and choose the config file from the test bench cell. Use the stimuli button to create the stimuli (copy the stimuli from the schematic simulation) for the test, and then run it.

If you want to simulate corners with the ptap1 and ntap1 components, you have to add two additional model files for your corner simulation. These model files for IHP 130nm process is located in /eda/design_kits/ihp_sg13/SG13S_618_rev1.12.0/tech/SG13_PASSIVES/spectre/

Add SG13_cornerCAP.scs and SG13_cornerRES.scs to your model files and click ok. Now you can add bcs(Best Case Scenario) and wcs (Worst Case Scenario) to each corner, remember to enable the "tick box" for each of them. When you are done, the corner setup should look something like this: