Bitvis UVVM VHDL Verification Component Framework: Difference between revisions

No edit summary |

No edit summary |

||

| Line 27: | Line 27: | ||

=== IRQC === | === IRQC === | ||

The provided interrupt controller | [[File:irqc.png|thumb]] | ||

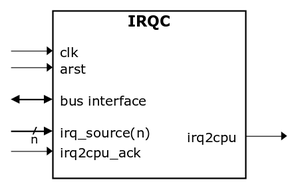

The provided example VHDL design is a simple interrupt controller with several internal registers, a bus interface and some input and output signals. | |||

[[File:irqc2.png|350px]] | |||

== Testbench creation == | == Testbench creation == | ||

Revision as of 14:56, 26 January 2016

-- Copyright (c) 2016 by Bitvis AS. All rights reserved. -- You should have received a copy of the license file containing the MIT License (see LICENSE.TXT), if not, -- contact Bitvis AS <support@bitvis.no>. -- UVVM AND ANY PART THEREOF ARE PROVIDED "AS IS", WITHOUT WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, -- INCLUDING BUT NOT LIMITED TO THE WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE AND NONINFRINGEMENT. -- IN NO EVENT SHALL THE AUTHORS OR COPYRIGHT HOLDERS BE LIABLE FOR ANY CLAIM, DAMAGES OR OTHER LIABILITY, -- WHETHER IN AN ACTION OF CONTRACT, TORT OR OTHERWISE, ARISING FROM, OUT OF OR IN CONNECTION WITH UVVM. --========================================================================================================================

Introduction

Bitvis UVVM VVC Framework is a complete framework for making VHDL testbenches for verification of FPGA and ASIC desing. You can download the complete code-base, examples and simulations scripts from the Bitvis web page.

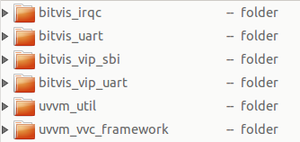

What's in the folders?

The download includes severals folders:

- bitvis_irqc - example VHDL design + testbench

- bitvis_uart - example VHDL design + testbench

- bitvis_vip_sbi - Verification IP(VIP) for simple bus interface(SBI)

- bitvis_vip_uart - VIP for UART TX and RX

- uvvm_util - UVVM utility library - sufficient for simple testbenches

- uvvm_vvc_framework - Framework for more advanced tutorials

IRQC

The provided example VHDL design is a simple interrupt controller with several internal registers, a bus interface and some input and output signals.

Testbench creation

Generate TB entity

Add support process for clock generation

Add test sequencer process

Copy the bitvis_irqc, bitvis_vip_sbi and uvvm_util to another location before editing the files.

Open up Questa/Modelsim

Change directory to the script folder (obviously change to your folder.....):

cd ~/phys321/bitviswiki/bitvis_irqc/script do compile_and_sim_all.do