## Department of physics and technology

## Development of the ALICE Busy Box

**Masters thesis**

by

Magne Munkejord

**University of Bergen October 2007**

#### **Abstract**

The European Organisation for Nuclear Research (CERN) is building a large circular particle accelerator called the Large Hadron Collider (LHC). The LHC will be able to accelerate and contain two beams of particles, travelling in opposite directions around the accelerator ring.

At four points around the ring the beams will intersect and the accelerated particles will collide. Four large detector experiments are being constructed around these points to observe the collisions.

The ALICE experiment is designed to study the effects of large hadrons colliding at very high energies. Collisions will occur with a average rate of approximately 8 kHz. Only a subset of these collisions provide interesting data and a sophisticated trigger system is employed to select which events should be recorded.

The Front End Electronics (FEE) of the detector sub systems produces large amounts of data for each event that is recorded. The event data is transferred out of the detector and up to the Data Acquisition (DAQ) system over high speed optical fiber links.

The Busy Box is a FPGA based device that monitors and verifies the transfer of event data from the FEE to the DAQ system of the ALICE experiment at CERN. By looking at which events have been triggered for readout and which of these events have arrived at the DAQ the Busy Box keeps track of the number of used buffers in the FEE. The Busy Box will assert a busy signal to let the trigger system know if the buffers run full and thereby prevent additional triggers and a possible overflow and data corruption in the buffers of the FEE. This feature makes it possible to run the system at its maximum capacity concerning the readout bandwidth from the FEE to the DAQ system where the busy generation will reduce the trigger rate whenever the bandwidth is insufficient.

The Busy Box will be utilized to four of the sub detector systems of ALICE; PHOS, EMCal, FMD and the Time Projection Chamber (TPC). For the TPC sub detector system the Busy Box needs to communicate with over 200 units in the DAQ system to verify the transfer of each event. The process of event transfer verification must execute significantly faster than the maximum readout rate of the detector which could reach a kHz.

#### Acknowledgements

The work presented in this thesis has been carried out with the help and support of many people. Most of them are employees or students at the Department of Physics and Technology at the University of Bergen where I spent my time as a master student.

First of all I would like to thank my supervisor Kjetil Ullaland for his guidance and support during this work. Dieter Röhrich deserves credit for sharing his wisdom and knowledge with me.

I want to thank Johan Alme and Ketil Røed for discussions and feedback on my work, and for their great help whenever I got stuck. Are Stangeland has been a great co-student and travel companion on our trip to CERN. And from CERN I would like to thank Csaba Soós for his company and for his work with integrating and testing of the Busy Box.

Big thanks to my friends and co-students Yngve Skogseide, Edvard Fosdahl, Knut Solvåg, Olav Torheim, Thomas Gundersen and Anders Rossebø for times well spent at room 446 — the microelectronics lab.

Finally I would like to thank my parents, Kari and Einar, other family and friends for motivation and support.

# **Contents**

| 1 | Intr | oduction                                                         | 1  |

|---|------|------------------------------------------------------------------|----|

|   | 1.1  | European Organisation for Nuclear Research (CERN)                | 1  |

|   | 1.2  | The Large Hadron Collider (LHC)                                  |    |

|   | 1.3  | Collision rates in the LHC                                       | 3  |

|   | 1.4  | A Large Ion Collider Experiment (ALICE)                          | 4  |

|   | 1.5  | Time Projection Chamber (TPC)                                    | 5  |

| 2 | Data | a acquisition for ALICE TPC                                      | 7  |

|   | 2.1  | Introduction                                                     | 7  |

|   | 2.2  | Front End Electronics (FEE) of TPC                               | 8  |

|   |      | 2.2.1 Front End Card (FEC)                                       | 9  |

|   |      | 2.2.2 Readout Control Unit (RCU)                                 | 10 |

|   | 2.3  | Detector Data Link (DDL)                                         | 10 |

|   | 2.4  | Data Acquisition system                                          | 11 |

|   | 2.5  | Trigger system                                                   | 12 |

|   |      | 2.5.1 Central Trigger Processor (CTP)                            | 12 |

|   |      | 2.5.2 Trigger sequences                                          | 12 |

|   |      | 2.5.3 Past-future protection                                     | 13 |

|   |      | 2.5.4 Timing, Trigger and Control (TTC)                          | 13 |

|   |      | 2.5.5 Event ID                                                   | 13 |

|   | 2.6  | Busy generation                                                  | 14 |

|   | 2.7  | About this work                                                  | 14 |

| 3 | Busy | y Box                                                            | 17 |

|   | 3.1  | Busy Box hardware                                                | 17 |

|   | 3.2  | System overview                                                  | 18 |

|   | 3.3  | DCS board                                                        | 21 |

|   |      | 3.3.1 Trigger message decoding                                   | 21 |

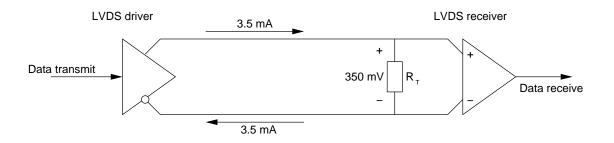

|   | 3.4  | Low Voltage Differential Signaling (LVDS) driver for BUSY signal | 21 |

|   | 3.5  | Virtex-4 Field Programmable Gate Array (FPGA)                    | 22 |

|   |      | 3.5.1 Virtex-4 I/O banks                                         |    |

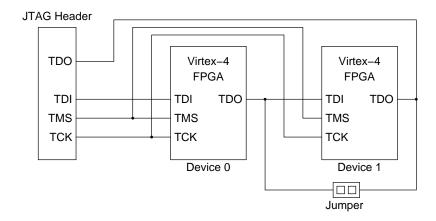

|   | 3.6  | Virtex-4 Programming Interfaces                                  | 22 |

|   |      | 3.6.1 SelectMAP interface                                        |    |

ii CONTENTS

| 3.7   | Busy Box circuit board                                                  | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-------|-------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

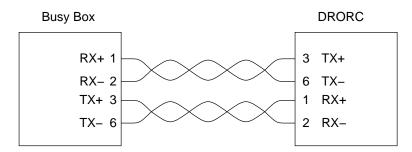

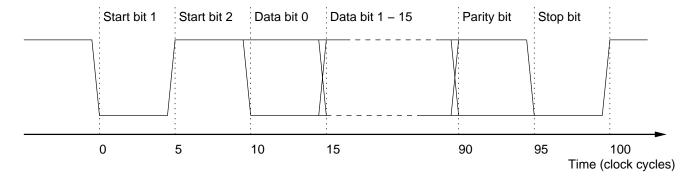

| Seria | al Communication with the D-RORCs                                       | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 4.1   | Physical Laver                                                          | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 4.2   | ·                                                                       | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|       |                                                                         | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|       |                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|       |                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 4.6   | · · · · · · · · · · · · · · · · · · ·                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Imn   | lomentation 3'                                                          | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| _     |                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|       |                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|       |                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|       |                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 5.4   |                                                                         | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|       |                                                                         | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| ~ ~   | · · ·                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 5.5   |                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|       |                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|       |                                                                         | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|       | •                                                                       | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|       | 66.                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|       |                                                                         | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|       | , 8                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 5.10  | Control and status registers                                            | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Testi | ing and verification 4                                                  | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 6.1   | Simulation                                                              | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|       | 6.1.1 Simulating the Busy Box firmware                                  | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 6.2   |                                                                         | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|       | 6.2.1 Loopback cable test                                               | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|       |                                                                         | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|       | <del>_</del>                                                            | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 6.3   |                                                                         | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|       | C                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Disc  | ussion and conclusion 5                                                 | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|       |                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|       | 1                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|       |                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|       |                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|       | Seria 4.1 4.2 4.3 4.4 4.5 4.6  Impl 5.1 5.2 5.3 5.4  5.5  Testi 6.1 6.2 | 3.7.1 Busy Box circuit board       2.         3.7.1 Power supply       2.         Serial Communication with the D-RORCs       2.         4.1 Physical Layer       2.         4.2 Serial bit-encoding schemes       2.         4.3 Alternative solutions       2.         4.4 Basic operation       2.         4.5 Transmission error handling       3.         4.6 Messages       3.         Implementation       3.         5.1 Introduction       3.         5.2 Overview       3.         5.3 DCS bus arbiter and address decoder       3.         5.4 Receiver module       4.         5.4.1 Serial Receiver       4.         5.4.2 Multiplexer tree architecture       4.         5.5.1 Serial encoder       4.         5.5.2 Transmitter module       4.         5.5.2 Transmitter controller       4.         5.6 RX Memory module       4.         5.7 Trigger receiver module       4.         5.8 Event ID verification module       4.         5.8 Event ID verification module       4.         5.9 Busy generator       4.         5.10 Control and status registers       4.         Testing and verification         6.1 Simula |

CONTENTS

|   | 7.5  | Conclusion                                      | 57 |

|---|------|-------------------------------------------------|----|

| A | Firn | ware for readout electronics of a muon detector | 59 |

|   | A.1  | Introduction                                    | 59 |

|   | A.2  | Cosmic rays                                     | 59 |

|   |      | A.2.1 Air showers and muons                     | 60 |

|   |      | A.2.2 Muon detection                            | 60 |

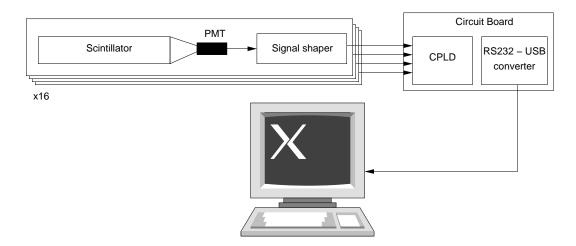

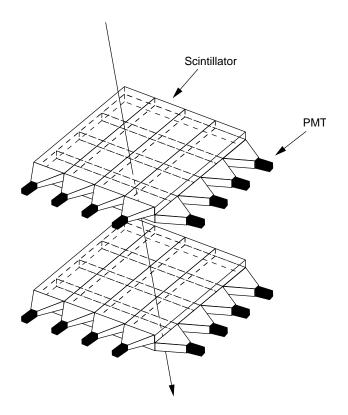

|   | A.3  | The Cosmic Ray Telescope detector system        | 60 |

|   |      | A.3.1 Scintillator                              | 60 |

|   |      | A.3.2 PhotoMultiplier Tube                      | 61 |

|   |      | A.3.3 Asynchronous trigger circuits             | 63 |

|   |      | A.3.4 Digital readout electronics               | 63 |

|   |      | A.3.5 Data analysis and presentation            | 64 |

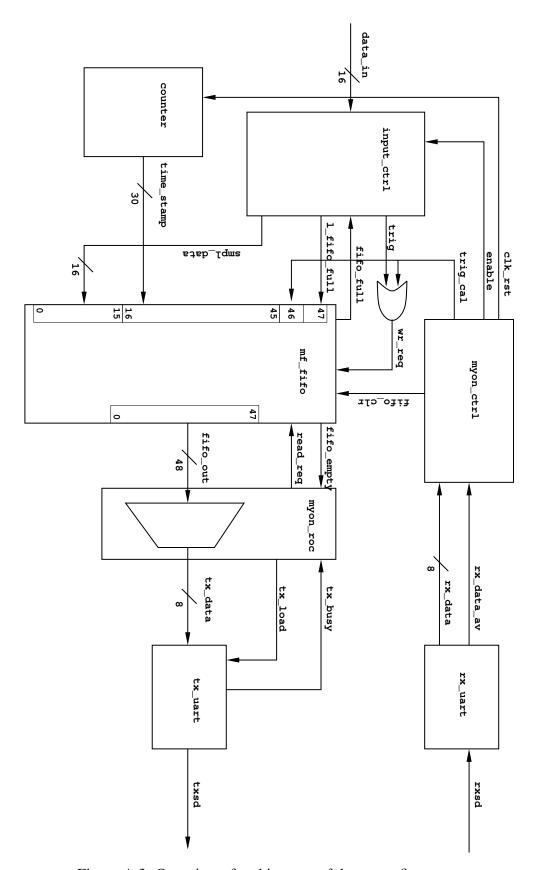

|   | A.4  | Firmware implementation                         | 64 |

|   |      | A.4.1 Overview                                  | 64 |

|   |      | A.4.2 Implementation                            | 65 |

|   | A.5  | Testing                                         | 66 |

|   |      | A.5.1 Simulation - Formal verification          | 66 |

|   |      | A.5.2 Synthesis and post-synthesis simulation   | 67 |

|   |      | A.5.3 Testing in real system                    | 67 |

|   | A.6  | Conclusion                                      | 67 |

| В | FPG  | Aworld 2007 article                             | 69 |

| C | Abb  | reviations                                      | 77 |

<u>iv</u> CONTENTS

# **Chapter 1**

## Introduction

## 1.1 European Organisation for Nuclear Research (CERN)

CERN is the European organization for nuclear research. It was founded in 1954 after World War II as a cooperation between 12 European countries to promote nuclear research. Today there are 20 nations that have status as members while several other nations and organizations have observer status. The organization makes it possible to build large experiments that would be too expensive for one nation alone.

CERN's facilities are located at the border between France and Switzerland, about an hours drive from Geneva. About 3000 full time employees runs and develop the facilities while some 6500 researchers and scientists spends time there to research.

## **1.2** The Large Hadron Collider (LHC)

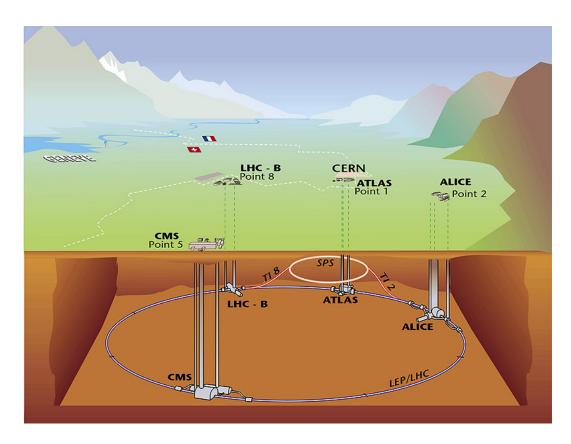

The LHC [1] is a large particle accelerator currently under construction at CERN's facilities. When it is finished it will be the largest and most powerful human built particle accelerator in the world. LHC is circular accelerator with a circumference of approximately 27 km. It is built in a tunnel that is 100 to 150 meters underground. The accelerator will be able to accelerate protons and heavy ions up to 99,9 % of the speed of light. Thus the particles will do approximately 11000 round trips in the accelerator per second. Figure 1.1 shows an illustration of the construction.

The particles are accelerated in several steps in other accelerators before bunches of particles are injected into the LHC where they will be accelerated up to their maximum velocity. The charged particles are accelerated by strong electric fields. The fields are generated by shooting electromagnetic waves into resonance cavities which oscillates at 40.08 MHz. This way particles of the same charge can be accelerated in both directions as long as they are in the electric field at the right time. What is important to note is that most of the bunches will be empty. Hence the actual rate at which bunches passes each other is lower than the nominal bunchcrossing rate of 40.08 MHz.

Two beams made up of particle bunches are accelerated in opposite directions around the accelerator ring. The two beams will travel in separate vacuum pipes so that there will not be

2 Introduction

Figure 1.1: Illustration of the LHC tunnel under CERN facilities on the border between Switzerland and France [1].

any other particles to collide with. The particles are kept in their orbit by strong magnetic fields that are generated by supercooled and superconducting magnets.

At four points around the accelerator ring the beams intersect and when bunches of particles crosses each others paths some of them might collide. In other words there is only a statistical probability that a bunchcrossing will result in a collision. As the particles collide the number of particles in each bunch decreases and thus the probability for collisions which ultimately reduces the collision rate. Since it is impossible to refill the bunches, the accelerator must be emptied when the collision rate is to low. A typical LHC run will last about 6-7 hours before the system must be restarted.

The reason for building the LHC is to be able to recreate physical processes that are known to happen out in the universe. Large detector systems are required to observe these events and therefor it is necessary to recreate them in a laboratory to be able to study them. Even though the energies in the collisions in the LHC will be the highest ever in man-built accelerators they are relatively low compared to the energies of particles observed in the cosmic radiation from far out in the universe. These particles have been created by processes like supernovas and the creations of black holes. It is expected that the results from research involving the LHC will illuminate these processes and other mysteries like the dark matter, anti matter and super symmetry.

Researchers hope that the energy density in the LHC collisions will be high enough to create Quark-Gluon-Plasma (QGP). Nucleons are made of quarks that are bound together be the strong force which is carried by particles called gluons. QGP is believed to be a state of matter where the quarks and gluons move freely. It is believed that all matter existed in this state 10 to 30 µs after the *Big Bang* [2]. By studying matter in this state scientist will be able to put existing theories to the test and to better understand what matter is and how the elementary forces interact.

The QGP will quickly expand and as the energy density decreases the quarks in the plasma will recombine into new particles that are spread out in all directions. These new secondary particles can be detected and will bring a lot of information about what happened in the collision. Very large and advanced detector systems are required to obtain the desired information and six different detector experiments are built around the points where the LHC beams intersect.

#### 1.3 Collision rates in the LHC

The rate at which collisions occur inside the detector depends on many factors. As described earlier the particles travel in bunches. For a collision to occur two bunches must cross paths in the detector. The rate at which this happens depends of many bunches have been injected into the LHC. This number is higher for proton-proton mode than Pb-Pb mode. The probability that some particles in two crossing bunches collide depends among other things on how many particles are in the bunches. After a while the number of particles in each bunch will be reduced as particles collide.

Another factor is the focus of the beams. Since the particles in the bunches have the same electric charge they will repel each other. The keep the bunches together the beams focused several places around the LHC. At the places where the beams intersect it is possible to adjust the focus of the beams so the collision rate to some extent can be controlled.

4 Introduction

## **1.4** A Large Ion Collider Experiment (ALICE)

As mentioned, the ALICE detector experiment is optimized to study heavy ion collisions (Pb-Pb<sup>1</sup>) but also proton-proton collisions will be studied. The main goal for the ALICE experiment is to prove the creation of and study the QGP.

When heavy ions collide in ALICE it is expected that tens of thousands of new particles will be created and pass through the detector system. The ALICE detector system must be able to track and identify most of them.

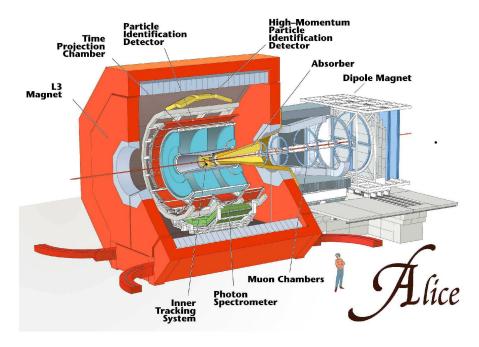

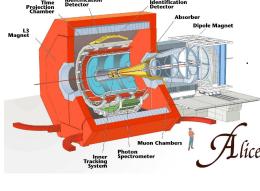

Figure 1.2: Illustrasjon av ALICE

The illustration in figure 1.2 shows an overview of ALICE. The beams are represented by a thin line through the detector and the particles will collide in the middle of the detector. ALICE consists of many sub detector systems. All the sub systems that are built around the collision point are called the central barrel detectors. In addition there are several sub detector systems in front and back of the central barrel detectors. These are used to determine trigger conditions.

The ALICE central barrel detectors [3]:

**Inner Tracking System (ITS)** Six layers of silicon wrapped around the beam pipe. It is capable of tracking particles with low momentum that does not reach out to the other detectors.

**Time Projection Chamber (TPC)** The main tracking detector of ALICE. Can reconstruct a 3D image of the trajectories of charged particles that passes through it.

Transition Radiation Detector (TRD) Can detect electrons and positrons.

<sup>&</sup>lt;sup>1</sup>Pb is the symbol for lead in the periodic table of elements.

**Photon Spectrometer (PHOS)** Based on lead tungstate scintillator crystals. Can detect photons.

**High Momentum Particle Identification Detector (HMPID)** Can detect particles with high momentum (fast moving particles).

**Time Of Flight (TOF)** Detects particles as they pass and measure the time-of-flight from the origin of the collision.

A large solenoid magnet (L3 magnet) is built around the central barrel detectors. This magnet will create a uniform homogeneous magnetic field parallel to the beams. When a charged particle travel through this field its trajectory will be curved depending on the particles charge and momentum.

### 1.5 Time Projection Chamber (TPC)

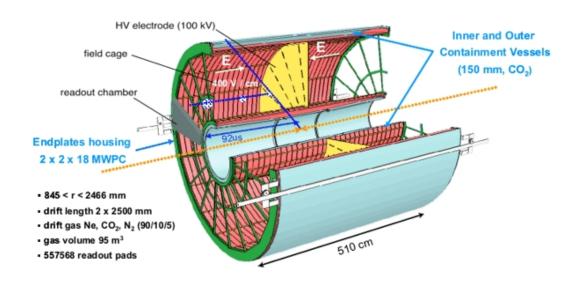

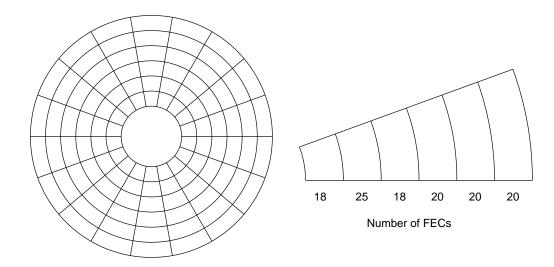

The TPC [4] is constructed as two coaxial cylinders around the collision point (the ITS will be placed inside the TPC). An illustration of the TPC structure is shown in figure 1.3. The volume between the cylinders is filled with gas². At the axial center the chamber is divided in two by a thin aluminized Mylar foil which acts as an electrode. The electrical potential of electrode is approximately 100 kV lower than the end caps of the chamber which creates electrostatic fields from the end caps towards the center electrode. When a charged particle travels through the chamber it will ionize the gas molecules in its path. The result is a trail of freed electrons and gas ions. The electric field makes the ionized gas molecules to drift towards the center electrode and the freed electrons towards the end caps of the chamber. As the electrons reach the end caps they can be detected as electrical charges. The time and position where the charges are detected on the end caps makes it possible to reconstruct a 3D image of all the particle trajectories in the chamber.

The charge of a single electron is to small to be detected without being lost in noise. To amplify the charges Multi-Wire Proportional Chambers (MWPCs) are used. Each end cap of the chamber is segmented in 18 sectors and each sector consists a inner and outer readout chamber (MWPC). See figure 1.3. Thin metal strings are stretched out in parallel so that they make up a plane. There are three such planes in each readout chamber. By applying different voltages to the wire planes strong electric fields are created. These fields are much stronger than the field in the rest of the chamber. When the drifting electrons enter readout chambers they are accelerated so that they gain enough energy to ionize gas molecules. The process is repeated for the electrons that are freed and a avalanche of electrons will eventually hit the end cap. The reason for using three wire planes is to be able to close the readout chambers by applying a voltage to the gating grid (first wire plane from the center of the chamber) so that the incoming drifting electrons are absorbed and will not reach the end caps.

$<sup>^2</sup>$ The gas mixture is normally 90% Neon and 10% CO $_2$  but can be altered to adjust the properties of the detector. Recently it has been proposed to add 5% N $_2$  [4].

6 Introduction

Figure 1.3: Illustration of the Time Projection Chamber [4].

To obtain to position where the electrons hit the end caps of the chamber, each end cap is divided into pads. In total the TPC has approximately 560000 pads where charges can be detected. Each pad or channel is sampled and readout by electronics that will be described in the next chapter.

A lot of information can be obtained about the particles that has travelled through the TPC by studying their tracks. When charged particles moves in a magnetic field they will experience a force perpendicular to their direction of movement. In addition the particles will loose speed as they ionize gas molecules. These two effects will cause the trajectories of the particles to be bent and with a sharper curve as the particle looses speed. By analyzing the tracks it is possible to determine momentum of the particles by looking at how much energy they loose per unit of travelled distance.

# **Chapter 2**

# **Data acquisition for ALICE TPC**

#### 2.1 Introduction

Data acquisition is the process of sampling the signals from the detector to obtain the desired information about the physical processes that are being observed. The ALICE data acquisition system acquires huge amounts of data for later analysis. Data are captured from the detectors at rates of hundreds of GB/s while the maximum rate of the permanent storage is 1.2 GB/s. One of the challenges of the data acquisition system is to filter and select which data should be kept and stored.

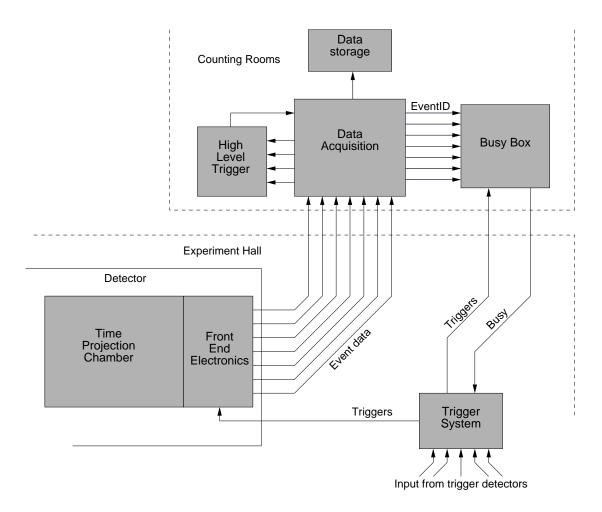

There are three main components in play for the ALICE data acquisition:

- **Front End Electronics (FEE)** Includes all electronics that sits directly connected to the detectors. It samples and digitizes the detector signals, performs some signal processing, buffer and push data to the DAQ-system.

- **Data Acquisition (DAQ) system** This system receives the data streams from the FEE. The captured data is transmitted in optical fiber channels from the detector and up to the DAQ receivers which are located in the counting rooms.

- **Trigger system** Initiates the data capture in the FEE makes sure that only the most interesting events are readout and pushed to the DAQ system. All events that are readout will be labeled by the trigger system. It is crucial for the coordination of the sub detector systems of ALICE and controlling the data flow.

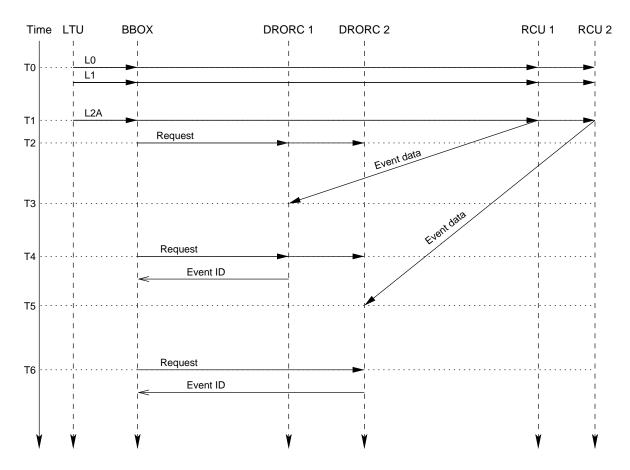

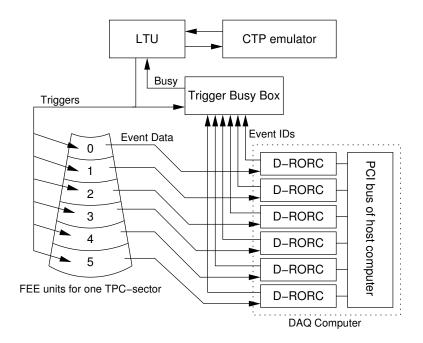

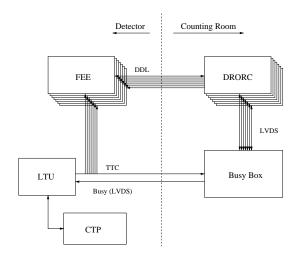

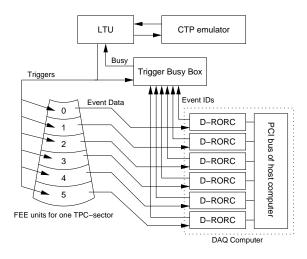

The schematic diagram in figure 2.1 gives an overview of the system but it includes only the readout chain of the TPC detector. The readout chains of the other sub detector systems that are planned to utilize a Busy Box are identical. The Busy Box is a system whose purpose is to verify the data transfer from the FEE to the DAQ system and to prevent overflow in the buffers of the FEE. The purpose and functionality of the Busy Box and the other components will be elaborated in the following sections.

Figure 2.1: Illustration of the data flow and the trigger system for the ALICE TPC.

The counting rooms, where some of the components are located, are compartment crates that are placed in the vertical tunnel down to the experiment hall of ALICE. The counting rooms will not be exposed to ionizing radiation from the collisons as all the components that are in the experiment hall will be. The FEE which is located inside the L3 magnet must also deal with the magnetic field. No materials wih magnetic properties can be used inside the L3 magnet.

## 2.2 Front End Electronics (FEE) of TPC

The data acquisition starts at the FEE. The two endcaps of the TPC contains 557568 pads in total. When the trigger system confirms a collision in the detector by issuing a Level 1 trigger, the analog signals from these pads are sampled and digitized by the FEE. To capture a complete event the FEE of the TPC must sample the detector signals from the pads during the entire drift time of the TPC which is approximately  $100 \mu s$ .

Each endcap is divided into 18 sectors and each sector is divided into 6 patches as shown in

Figure 2.2: The end cap of the TPC divided into sectors and patches.

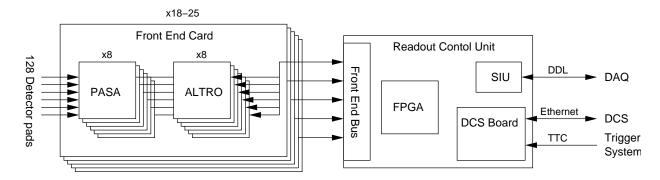

Figure 2.3: Schematic overview of the components of the Front End Electronics of the Time Projection Chamber.

figure 2.2. Figure 2.3 shows an overview of the components of the FEE that are applied to each patch. In total the TPC has 216 patches.

#### 2.2.1 Front End Card (FEC)

The FEC is a circuit board that hosts a number of Integrated Circuits (ICs) to sample, digitize, process and buffer signals from the pads. The number of FECs used for each patch is shown in figure 2.2. As can be seen in the figure the density of FECs, and thus pads, varies and the pad density is highest in the innermost patches of the sector. This is because the track density will be higher in this region and a higher resolution is thus required to be able to reconstruct the event properly in this region.

There are two different Application Specific Integrated Circuits (ASICs) involved in the data chain. The Preamplifier and Shaper ASIC (PASA) is an analog ASIC that amplifies and shapes

the raw signals from the pads before they are sampled by the ALICE TPC ReadOut (ALTRO) chip [5]. The ALTRO chip is an mixed signal ASIC with integrated 10 bit Analog to Digital Converters (ADCs) and will sample the signals at 5 or 10 MHz rate. The samples are run run through a pipeline where signal processing is performed in five steps before the data are stored in on-chip memory. The signal processing includes baseline reduction, 3rd order digital filtering and zero suppression. The ALTRO can buffer up to 4 or 8 events depending on the sample rate but independent of the data reduction. Even if the signal processing reduces the event data size to a tenth of the original size the event will still occupy one buffer slot [6].

Each PASA and ALTRO chip can operate on 16 channels independently. Each FEC hosts eight pairs of these chips and is able to capture signals from 128 channels and in total 4356 FECs are used for the ALICE TPC.

#### 2.2.2 Readout Control Unit (RCU)

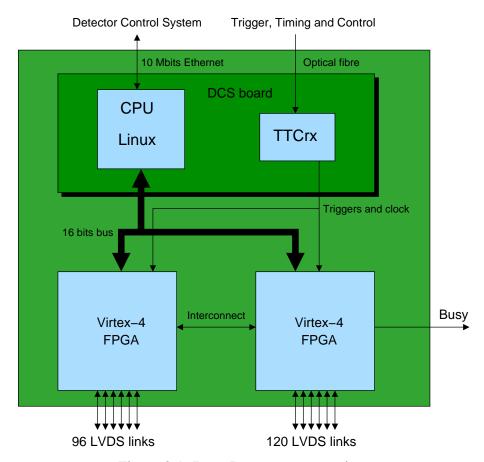

As the name implies the RCU is responsible for controlling the operation of the FECs and the readout from the FEC buffers to the DAQ system. There is one RCU for each patch on the TPC, resulting in 216 RCU boards. The RCU is based on FPGA technology and interfaces with the FECs, DAQ, Detector Control System (DCS) and the trigger system.

The RCU will decode the triggers received via the TTC system and forward the triggers to control the FECs. As outlined earlier, the FEC of the TPC should initiate data capture upon reception of a Level 1 trigger and the current buffer should be flagged for transmission to the DAQ system if the sequence ends with a Level 2 Accept message. The RCU will continuously, event-by-event, readout the flagged buffers from the ALTROs and transfer them to the DAQ system via the DDL system. For each event that is transfered to the DAQ system the RCU prepends a Common Data Header (CDH). The CDH contains information about the corresponding trigger sequence, including the event ID.

In addition to controlling the data capture and the readout to DAQ, the RCU is also responsible for configuring and monitoring the FEE. The configuration data can be sent to the RCU in one of two ways. Either via the DCS system or via the DDL system.

Access to the FECs is provided by a bus, named the Front End Bus. The Bus is composed of 40 bi-directional lines and 8 control lines [5]. The data are sent to DAQ with a Source Interface Unit (SIU) optical data adapter, described in section 2.3. The SIU is mounted on the RCU board as an add-on card. The RCU will continuously read the buffers of the ALTROs and transmit the content to DAQ.

## 2.3 Detector Data Link (DDL)

The DDL utilizes optical fibers to transfer data at high rates from the FEE to the DAQ system. One link contains two fiber channels and can transfer 200 MB/s in both directions simultaneously. ALICE uses almost 400 DDLs where 216 out of these are used for the TPC [7]. The DDL system can also be used to transfer configuration data to the FEE.

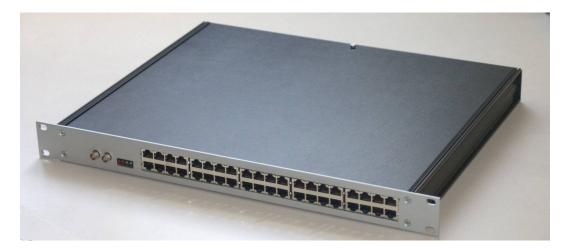

Figure 2.4: Picture of the D-RORC with two optical transceivers (SIU/DIU) and two LVDS ports.

The DDL system is composed of three parts; the optical fibers, a SIU and a Destination Interface Unit (DIU) [7]. The SIU units are mounted on the RCU boards and the DIU units are mounted on special receiver cards for the DAQ.

## 2.4 Data Acquisition system

On the DAQ side, special Read Out Receiver Cards (RORCs) have been designed to receive the data from DDL. The RORC includes one or two DIUs and is designed as PC card with a Peripheral Component Interconnect (PCI) interface. Up to six of these cards can be installed in a regular computer called a Local Data Concentrator (LDC). The use of commercial hardware is very desirable because it reduces the total costs of the system considerably. The RORC utilizes its own Direct Memory Access (DMA) controller to write data directly to the main memory of its host computer with a minimum load on the Central Processing Unit (CPU) [8].

The RORC exists in two different versions, the pRORC and the DAQ Read Out Receiver Card (D-RORC). The pRORC has only one DIU while the D-RORC have two. Figure 2.4 shows a picture of the D-RORC. When receiving data from a sub detector whose data is to be analyzed by the High Level Trigger (HLT), the extra DIU on the D-RORC will be used as a SIU and the incoming data will be copied and transferred to the HLT [9].

Computers with RORCs are called LDCs. They will merge event data fragments from the D-RORCs to sub-events. Through a network of computers the sub events are merged until they reach the Global Data Concentrator (GDC) where the event data will be complete. From here the data will be transferred to CERN's storage facility for permanent storage and later analysis [10].

The data transfer from the RCU to the D-RORC will go on as long as there is event data in the buffers. However the capacity of the event building network may get saturated. In this case the RCU will see the DDL link as busy and the transmission must wait even if there are more data to be shipped [11].

| Signal Status              | L0 (μs) | L1 (μs) | L2 (μs) |

|----------------------------|---------|---------|---------|

| Last trigger input at CTP  | 0.8     | 6.1     | 87.6    |

| Trigger output at CTP      | 0.9     | 6.2     | 87.7    |

| Trigger output at detector | 1.2     | 6.5     | 88.0    |

Table 2.1: Latencies associated with different trigger levels in the CTP.

### 2.5 Trigger system

The trigger system will make sure that the FEE only captures data when interesting events occurs in the detector. By issuing different triggers the system can start, abort and verify data capturing of events in the FEE. The sub detector systems of ALICE are arranged in to six clusters. The trigger system can be configured to only trigger data capture in only a subset of these clusters [9]. The CTP is the source of all the hardware triggers in ALICE. It is placed in the same racks as the Local Trigger Units (LTUs) for the detectors in the experiment hall. The LTUs will forward the triggers from the CTP to the FEE of their detector systems.

#### 2.5.1 Central Trigger Processor (CTP)

The CTP is located in the experiment hall, outside of the L3 magnet. Several sub detector systems feeds the CTP with the required information to make decisions about which triggers should be issued to the FEE. The CTP uses three levels of triggers to control the FEE: Level 0, Level 1 and Level 2 [9].

### 2.5.2 Trigger sequences

The triggers are issued in sequences. For a sequence to be valid it must follow the rules outlined in the following paragraphs.

The Level 0 trigger is the fastest of the triggers (see table 2.1) and must arrive at the detectors  $1.2~\mu s$  after the time of impact. The Level 0 trigger only indicates a collision in ALICE. Some detectors will start to capture data right away while others wait for the Level 1 trigger. For the TPC for example, it will take some time before the drifting electrons reach the endcaps and therefore the FEE will initiate data capture on a Level 1 trigger.

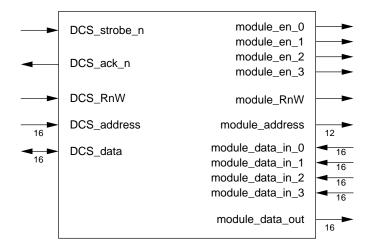

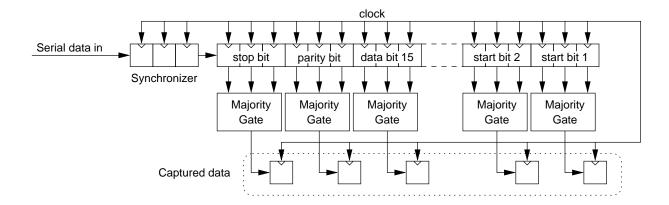

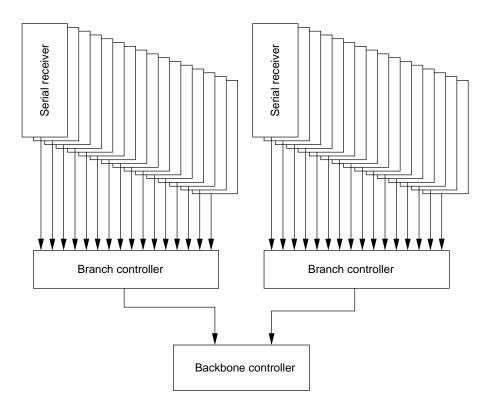

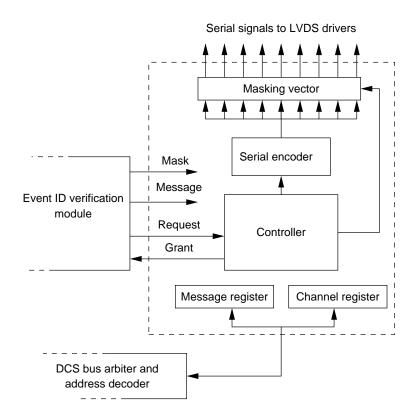

The Level 1 trigger must reach the FEE 6.5 µs after time of impact and confirms the collision that the Level 0 first indicated. The Level 1 is based on more physical parameters about the collision, for example the multiplicity of the collision. If the requirements for the Level 1 trigger is not met in the CTP, the Level 1 will not be issued. This results in a timeout for the Level 1 trigger in the detectors and the trigger sequence is aborted and hence data capture will be aborted in the detectors.