# BusyBox User Guide

The purpose of the BusyBox is to let the Central Trigger Processor (CTP) know when the FEE's buffers are full by asserting a busy signal which prevents further issuing of triggers. The BusyBox and D-RORCs receive a unique event ID from the FEE after an event. After a valid trigger sequence ends the BusyBox will ask the D-RORCs if they have received the same event ID as the BusyBox did. If they do not reply with the same ID it means data has not been shipped from the Fee to the D-RORC, hence, the buffer in the Fee still holds event data.

The BusyBoxes are located in the DAQ counting rom and is a FPGA based system developed at the University of Bergen. The first of three development phases was done by Anders Rossebø. He designed the BusyBox hardware including the 19" rack case. Then Magne Munkejord developed the firmware and PhD student Johan Alme contributed with the Trigger Receiver Module to make the firmware complete. And finally a full test, integration and commissioning was done by Rikard Bølgen and Magne Munkejord.

This User Guide is about the whole BusyBox system. The intention is to give newcomers to the system an intuitive understanding without going too much in detail.

The first part of this user manual is an overview of the BusyBox. Hardware, Firmware, DCS board and communication systems will be discussed. The second part is how to interact with everything. How to program and read registers in the FPGA, to emulate triggers from an emulator.

For more latest firmware relase and latest discussion about the BusyBox, check out the wiki at:

https://wikihost.uib.no/ift/index.php/Busy\_Box\_and\_related

| 1           | Table of content                                  |    |

|-------------|---------------------------------------------------|----|

| 1           | TABLE OF CONTENT                                  | 2  |

| 2           | INTRODUCTION                                      | 3  |

| 2.1         | Document History                                  |    |

| 2.2         | Abstract                                          |    |

| 3           | SYSTEM OVERVIEW                                   | 4  |

| 4           | BUSYBOX HARDWARE                                  |    |

| <b>4</b> .1 | Xilinx Virtex IV FPGA                             |    |

| 4.2         | DCS                                               |    |

| 5           | BUSYBOX FIRMWARE                                  |    |

| <i>5.1</i>  | Introduction                                      |    |

| 5.1<br>5.2  | BusyBox top-level wrappers                        |    |

| 5.2<br>5.3  | Module digital_clock_manager                      |    |

| 5.4         | Busylogic top Module                              |    |

| 5. <b>5</b> | Reset logic module                                |    |

| 5.6         | DCS Bus Arbiter and Address Decoder               |    |

| 5.7         | Receiver Module                                   |    |

| 5.8         | Transmitter Module                                |    |

| 5.9         | RX Memory Module                                  | _  |

| 5.10        | RX Memory Filter Module                           |    |

| 5.11        | Trigger Receiver Module                           |    |

| 5.12        | Event ID Verification Module                      |    |

| 5.13        | Busy Controller Module                            |    |

| 5.14        | Control and Status Registers                      |    |

| 6           | FUNCTIONAL VERIFICATION OF THE BUSYBOX FIRMWARE   |    |

| 6.1         | Introduction                                      |    |

| 6.2         | Support packages                                  |    |

| 6.3         | The RCU and DRORC emulator module                 |    |

| 6.4         | Testbench execution flow                          |    |

| 6.5         | Running the simulation in QuestaSim/ModelSim      |    |

| 7           | BUSYBOX DCS BOARD                                 |    |

| 7.1         | Setting up DCS board Firmware to use with BusyBox |    |

| 8           | BUSYBOX COMMUNICATION                             |    |

| 8.1         | BusyBox - DRORC Communication                     |    |

| 8.2         | TTCrx Communication                               |    |

| 8.3         | DCS Communication                                 |    |

| 8.4         | LTU Communication                                 |    |

| 9           | GETTING STARTED WITH THE BUSYBOX                  |    |

| 9.1         | Introduction                                      |    |

| 9.2         | SVN Repository and Project Setup                  | 50 |

| 9.3         | Hardware Setup                                    |    |

| 9.4         | Logging on to the DCS board                       |    |

| 9.5         | RCU Shell                                         |    |

| 9.6         | Programming the FPGA                              |    |

| 9.7         | Configuring the Firmware                          |    |

| 9.8         | Monitoring the BusyBox registers                  |    |

| 9.9         | Resetting the BusyBox                             | 53 |

| 9.10        | CTP Emulator                                      | 53 |

| <i>10</i>   | DECICRED                                          |    |

| 10          | REGISTER                                          | 55 |

| 10.1        | REGISTER BusyBox Register Interface               |    |

|             |                                                   | 55 |

#### 2 Introduction

The purpose of this document is to give users of the BusyBox an understanding of what it is, by discussing the hardware, firmware and software which is the key components of the ALICE BusyBox system.

The scope of this technical paper and user guide will be to collect all the information necessary to understand, use and modify the BusyBox.

#### 2.1 Document History

| Revision<br>number | Revision date | Summary of changes                                                                                                                                                                                                                                                         | Author          |

|--------------------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| 1.0                | 09.12.08      | N/A                                                                                                                                                                                                                                                                        | Rikard Bølgen   |

| 1.1                | 08.12.09      | <ul> <li>Merged into one file.</li> <li>Added chapter Feil! Fant ikke         referansekilden. Feil! Fant ikke         referansekilden. Changed document         style.</li> <li>Updated some interface tables and         figures to latest firmware revision.</li> </ul> | Magne Munkejord |

| 1.2                | 14.09 2010    | <ul><li>Updated first page</li><li>Edited layout</li></ul>                                                                                                                                                                                                                 | Kjetil Ullaland |

Table 2-1: Revision history.

| Package                 | Version              |

|-------------------------|----------------------|

| Firmware BusyBox        | 41                   |

| Trigger Receiver Module | 1.5                  |

| DCS card                | Version 2.84 BUSYBOX |

Table 2-2: Firmware versions corresponding to this guide.

#### 2.2 Abstract

ALICE is one of four large detectors situated at the collision points in the LHC at CERN. The BusyBox utilizes the TPC, PHOS, FMD and EMCal sub-detectors and it is an FPGA based device.

It will verify the transfer of event data from the sub-detectors Front End Electronics (FEE) to the Data Acquisition system (DAQ). The BusyBox also keeps track of free buffers in the FEE. If the buffers are full or a collision is detected the BusyBox will flag a busy signal to a Central Trigger Processor (CTP), which halts further triggers from being issued.

Interaction with the BusyBox is done through the DCS board, either via Ethernet or UART.

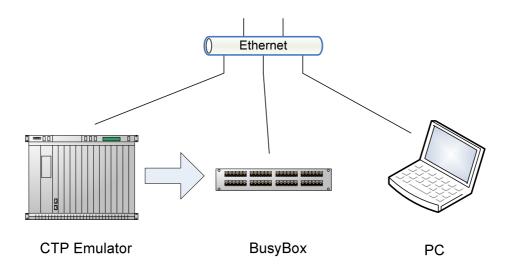

## 3 System Overview

The BusyBox is a part of the data acquisition in four of the ALICE sub-detectors, namely: TPC, PHOS, FMD and EMCal. The latter is currently in development.

There are some minor differences between the BusyBoxes for each sub-detector because of the different numbers of D-RORCs they use.

| Detector | D-RORCS | Panel height |

|----------|---------|--------------|

| TPC      | 216     | 5 units      |

| PHOS     | 20      | 1 unit       |

| FMD      | 24      | 1 unit       |

| EMCal    | 3       | 1 unit       |

Table 3-1: Number of D-RORCs per detector

Data acquisition in ALICE is trigger based and is controlled by a Central Trigger Processor (CTP). The CTP distributes a trigger sequence starting with a L0 trigger when it senses a collision. Then, depending on the quality of the collision a L1 followed by an L2a or L2r trigger is issued by the CTP via the LTU.

The TPC FEE starts buffering data upon receiving a L1 trigger and PHOS a L0 trigger. The FEE on the four subdetectors can buffer 4 or 8 events depending on number of samples configured.

So, the BB has two main tasks, keep track of available buffers and maintain a past-future protection. If the buffers are full or a L1 trigger is issued the BusyBox asserts a busy signal to the CTP, which will halt further triggers. The busy is then removed if these conditions are no longer true.

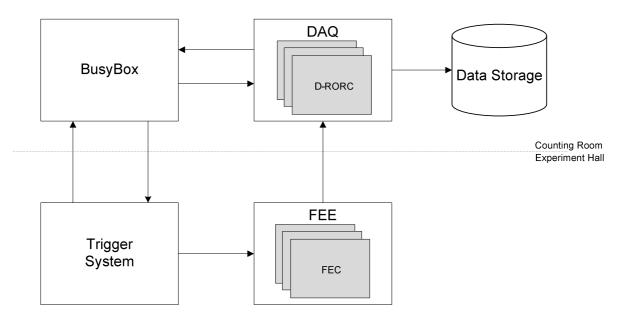

The BusyBox has no direct communication with the FEE and keeps track of available buffers by communicating with the D-RORCs. The Trigger System sends triggers to the BusyBox and the FEE. Figure 3-1 below illustrates the BusyBox place in the readout chain.

Figure 3-2: Illustration of the data flow for the BusyBox system. The BusyBox and D-RORCs are placed in the counting rooms above the experiment hall.

# 4 BusyBox Hardware

This chapter discusses the hardware and some key components.

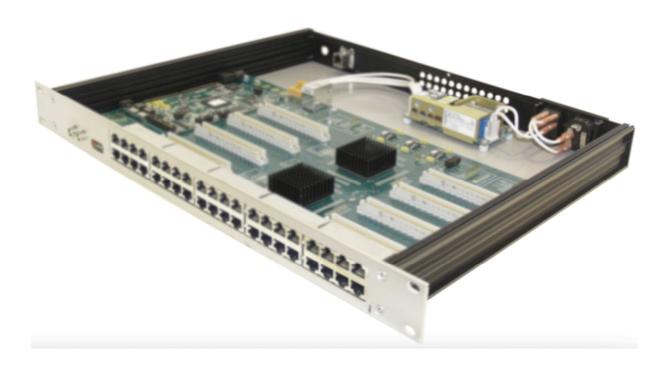

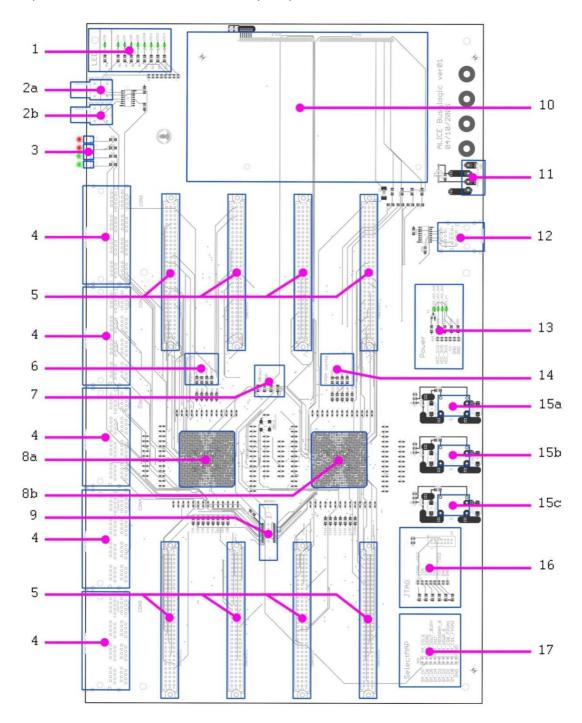

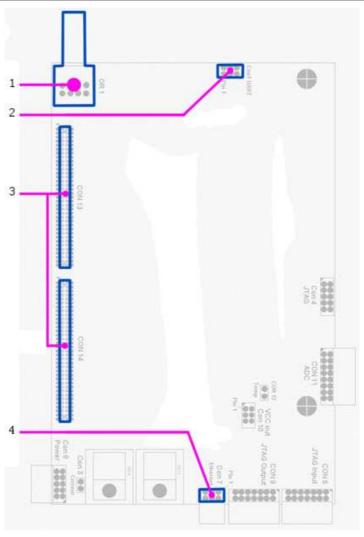

Figure 4-1 BusyBox PCB

| #     | Туре                           | Description                                                                         |

|-------|--------------------------------|-------------------------------------------------------------------------------------|

| 1     | LED indicators                 | Indicates numbers of buffers used                                                   |

| 2a    | LEMO contact                   | LVDS busy signal from FPGA 1                                                        |

| 2b    | LEME contact                   | LVDS busy signal from FPGA 1                                                        |

| 3     | LED indicators                 |                                                                                     |

| 4     | RJ-45 contact                  | RJ-45 contacts for D-RORCs                                                          |

| 5     | Mezzaine connectors            | Mezzaine card holders to additional RJ-45 connectors                                |

| 6     | Resistors                      | FPGA1 configuration resistors. Sets the configuration mode to 8bit SelectMAP slave. |

| 7     |                                |                                                                                     |

| 8a    | FPGA 1                         | Xilinx Virtex IV                                                                    |

| 8b    | FPGA 2                         | Xilinx Virtex IV (TPC only)                                                         |

| 9     |                                | Connector for digital analyzer. Also serves as inter connect between FPGAs          |

| 10    | DCS board                      | Connectors for DCS board                                                            |

| 11    | Power supply connector         | Connector for external power supply. Power supply: 5V, 12 A                         |

| 12    |                                | SelectMAP resistor for pull-ups/pulldowns and thevenin termination of clock (CCLK). |

| 13    | Pin connectors                 | GND, 1.2V, 2.5V and 3.3V output                                                     |

| 14    |                                | FPGA2 configuration resistors. Sets the configuration mode to 8bit SelectMAP slave. |

| 15abc | Voltage regulator              | PTH05000W voltage regulators from Texas Instruments                                 |

| 16    | Test point JTAG interface      | Standard JTAG access port. Used for configuration and debug.                        |

| 17    | Test point SelectMap interface | BUG: SelectMAP CCLK must be cut at certain point on PCB to prevent ringing.         |

Table 4-1: List of components on the PCB.

#### 4.1 Xilinx Virtex IV FPGA

The BusyBox use the Virtex-4 LX-40 with the ff1148 package from Xilinx. There are 640 user programmable I/O pins that support LVDS 2.5 standard used to communicate with the D-RORCs. The Virtex-4 can run on clock speeds up to 500 MHz, store 18 Kbits in 96 BRAM modules and has DCM to provide flexible clocking and synchronization.

A "Multiple device SelectMap bus" is used to program the FPGAs, since two FPGAs can be used with different firmware. Linux kernel device drivers have been developed so that the Linux OS running on the DCS board can redirect the programming bit file to the FPGA.

The BusyBox can also be programmed via JTAG interface on the PCB. When one FPGA is used a jumper on the PCB needs to be applied to bypass the missing JTAG chain.

#### 4.2 DCS

The DCS board was originally designed for the TRD and TPC sub-detectors, but because it was very versatile it has been adapted for the BusyBox and other instrumenst in ALICE experiment. It is running a lightweight version of Linux and implements TCP/IP network protocol. The DCS board has a TTCrx chip to receive the LHC clock, first level trigger accept and trigger messages. Each card runs a FEE server that interfaces with the system it is connected to. Thus, it makes it possible to program the FPGA(s) and read/write registers remotely from the control room at Point 2.

## 5 BusyBox Firmware

This chapter discusses the functionality of the firmware and gives a description of each module with sub-modules. The firmware modules are described with text, pictures, entities and port details.

#### 5.1 Introduction

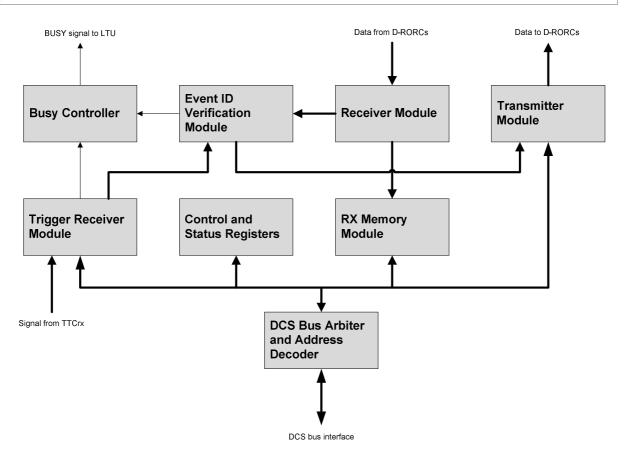

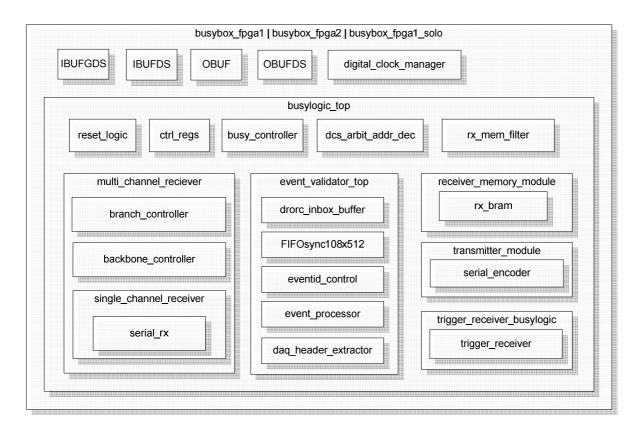

Figure 5-1: Main BusyBox firmware modules.

The firmware controls the BusyBox and executes its designed purpose based on inputs from three sources: TTCrx, BusyBox DCS card and the D-RORCs. The above figure shows the main firmware modules of the BusyBox and will be discussed in more detail. As mentioned before the BusyBox has two main functions: assert the busy signal if FEE buffers are full or when a L1 trigger has been issued by the CTP.

## 5.1.1 An intuitive explanation of how the BusyBox firmware works

It all starts with a collision of hadrons in the LHCs ALICE detector. The CTP detects this collision and notifies the LTU, which issues a LO trigger to all four BusyBoxes via its optical fiber network. The LO trigger is the start of a sequence of triggers and ends with either an L2a or L2r trigger.

The LTU broadcasts the BC, Channel A and Channel B to the BusyBox through its fiber network and is converted by the TTCrx chip, on the DCS card, to electrical signals. Then the information is decoded by the trigger receiver module.

Not all of the decoded messages are useful for the BusyBox. Hence, the trigger receiver module only extracts the bunch count, event ID and triggers.

The triggers are forwarded to the busy controller module, which asserts the busy when a L1 trigger is received.

The bunch count and event ID is used to assure that all D-RORCs have received data from an event and with that information in hand the BusyBox can keep track of the FEE buffers. If all D-RORCs have received event data, this will imply that the event data have been read out from the FEE buffers. It is the busy controller module that keeps track of the FEE buffers. FEE buffers can hold 4 or 8 events and starts buffering data on a L0 trigger (TPC starts on a L1). So if there is a L0 trigger 1 buffer is occupied, and if all the D-RORCs have responded with the same event ID and bunch count the EventID is OK (EIDOK). Then the event data have been read out and the buffer is free.

A control and status register can as the name implies, control and check the status of registers in the BusyBox.

Registers in the trigger receiver module and stored data from the receiver module in the RX memory module can also be accessed. All this is done via the FeeServer on the DCS card mounted on the BusyBox PCB.

#### 5.1.2 VHDL Entity Hierarchy

- busybox\_fpga1\_solo || busybox\_fpga1 || busybox\_fpga2

- busylogic\_top

- o ctrl regs (Control and Status Registers)

- dcs\_arbit\_addr\_dec (DCS Bus Arbiter and Address Decoder)

- transmitter\_module(Transmitter Module)

- serial\_encoder

- o multi channel receiver (Multi Channel Receiver Module)

- single\_channel\_receiver

- serial rx

- branch\_controller

- backbone controller

- o rx\_mem\_filter

- receiver\_memory\_module (RX Memory Module)

- rx\_bram

- o event validator top (Event ID Verification Module)

- drorc inbox buffer

- FIFOsync108x512

- daq\_header\_extractor

- eventid control

- eventid\_processor

- trigger\_receiver\_busylogic (Trigger Receiver Module)

- busy\_controller (Busy Controller)

The firmware can be implemented by using one of three different top-level wrappers. The different top-level wrappers are necessary to adapt the firmware to fit different hardware configurations. If two FPGAs are present then they must work in parallel and be coordinated. If only one FPGA is present it must operate in standalone mode.

Figure 5-2 shows a graphical representation of the same information as above. In addition the IO buffers that are instantiated in the top-level wrappers are included in the figure.

Figure 5-2: Module instantiation hierarchy.

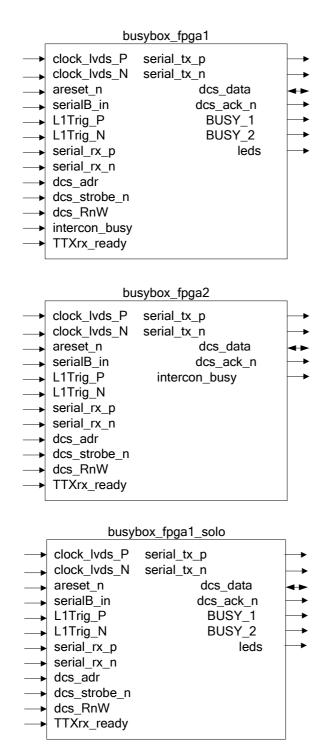

#### 5.2 BusyBox top-level wrappers

The BusyBox PCB can be fitted with one or two FPGAs depending on the number of channels required. The different hardware configurations require slightly modified versions of the firmware at the toplevel HDL source. A BUSY signal from FPGA2 is combined in FPGA1 among other things. There are three different toplevel HDL files: busybox\_fpga1.vhd, busybox\_fpga2 and busybox\_fpga1\_solo. There three are different usage scenarios:

- For BusyBoxes with 2 FPGAs mounted, FPGA1 should be programmed with firmware based on busybox\_fpga1 and FPGA with busybox\_fpga2.

- If the second FPGA is not going to be used then FPGA1 can be programmed with busybox\_fpga1\_solo, but FPGA2 must then be programmed with a dummy configuration for the programming operation to finish without errors.

- For BusyBoxes with only one FPGA firmware based on busybox\_fpga1\_solo must be used.

At the toplevel HDL wrappers it is possible to specify the number of channels to be implemented. Each channel is connected to the rest of the design through a branch. One branch controller can support up to 16 channels. There must be enough branches to connect the number of channels specified or the implementation will fail.

# 5.2.1 Entity BusyBox FPGA Modules

Acts as a wrapper for each version of the three firmware versions: busybox\_fpga1.vhd, busybox\_fpga2.vhd and busybox\_fpga1\_solo.vhd. These wrappers instantiates the BusyBox top module with the required generic parameters and extra logic. The wrapper also adds and configures the necessary Virtex-4 IO buffers and Digital Clock Manager (DCM) around the busylogic\_top module.

Figure 5-3: Entity for BusyBox FPGA modules.

BUSY1 and BUSY2 outputs only exist on FPGA1. These outputs are the same logical signal.

Busybox\_fpga1 wrapper takes busy input (intercon\_busy) from FPGA2 and combines it with its own BUSY output through an OR gate.

| Generic name    | Туре    | Legal range | Default value | Description                                                                                        |

|-----------------|---------|-------------|---------------|----------------------------------------------------------------------------------------------------|

| num_of_channels | natural | 0 to 119    | 119           | Specifies the number of channels (-1) that will be instantiated at compile-time.                   |

| num_of_branches | natural | 1 to 8      | 8             | Specifies number of branches at compile-time. Each branch can connect 16 serial receiver channels. |

Table 5-1: Generics at the HDL top-level wrappers.

| BusyBox wrapper    | num_of_channels | num_of_branches |

|--------------------|-----------------|-----------------|

| busybox_fpga1      | 119             | 8               |

| busybox_fpga2      | 96              | 6               |

| busybox_fpga1_solo | 39              | 3               |

Table 5-2: Default values for generic parameters for BusyBox wrappers.

| Port Name     | Direction                 | # Bit            | Description                                        |

|---------------|---------------------------|------------------|----------------------------------------------------|

| clock_lvds_P  | Input                     | 1                | std_logic;                                         |

| clock_lvds_N  | Input                     | 1                | std_logic;                                         |

| areset_n      | Input                     | 1                | std_logic;                                         |

| serialB_in    | Input                     | 1                | std_logic;                                         |

| L1Trig_P      | Input                     | 1                | std_logic;                                         |

| L1Trig_N      | Input                     | 1                | std_logic;                                         |

| serial_rx_p   | Input                     | 120 <sup>1</sup> | <pre>std_logic_vector(0 to num_of_channels);</pre> |

| serial_rx_n   | Input                     | 120              | <pre>std_logic_vector(0 to num_of_channels);</pre> |

| dcs_adr       | Input                     | 16               | std_logic_vector(15 downto 0);                     |

| dcs_strobe_n  | Input                     | 1                | std_logic                                          |

| dcs_RnW       | Input                     | 1                | std_logic;                                         |

| intercom_busy | Input/Output <sup>2</sup> | 1                | std_logic;                                         |

| serial_tx_p   | Output                    | 1                | std_logic_vector(0 to num_of_channels)             |

| serial_tx_n   | Output                    | 1                | std_logic_vector(0 to num_of_channels)             |

| dcs_data      | Bidirectional             | 16               | std_logic_vector(15 downto 0)                      |

| dcs_ack_n     | Output                    | 1                | std_logic;                                         |

| BUSY_1        | Output <sup>3</sup>       | 1                | std_logic;                                         |

| BUSY_2        | Output <sup>2</sup>       | 1                | std_logic;                                         |

| leds          | Output <sup>2</sup>       | 13               | std_logic_vector(1 to 13);                         |

Table 5-3: I/O details for BusyBox FPGA Modules.

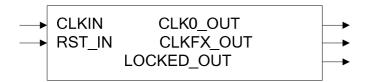

# 5.3 Module digital\_clock\_manager

This core has been generated by the Xilinx tool Architect Wizard available through the CoreGen GUI. It a single DCM configured to deskew and output two clock signals generated from the incoming clock. The incoming clock from the DCS board is approximately 40 MHz. The DCM multiplies this clock signal by 5 to generate a 200 MHz output used in the design. The 40MHz and 200 MHz are routed to global clock buffers that drive global clock nets to distribute the clock signals around the chips.

The DCM is setup in a system synchronous configuration. This means that the clock is fed back to the DCM after it has gone through the clock distribution network. The DCM will regulate the phase of its output clocks so that

<sup>&</sup>lt;sup>1</sup> Number of channels implemented is configurable.

<sup>&</sup>lt;sup>2</sup> This is an input on FPGA1 and an output on FPGA1. It does not exist in the busybox\_fpga1\_solo wrapper.

<sup>&</sup>lt;sup>3</sup> Only exists on FPGA1.

the feedback clock's rising edge and incoming's clock rising edge are aligned. This is done to compensate for the delay of the clock distribution network in the chip. This configuration ensures that the chip/FPGA is clocked synchronously with the rest of the system (other synchronous elements).

During startup of the FPGA (right after the configuration data has been loaded) the internal circuits of the DCM will try to lock on the incoming clock signal. This is an operation that might take several thousand clock cycles to complete and may fail if the incoming clock contains glitches and/or sporadic behavior. The clocks supplied by the DCM are not reliable until the DCM has acquired lock. A dedicated output signal named "lock" from the DCM indicates when lock has been acquired. This signal is forwarded to the reset logic which will hold the design in reset until the lock signal is deasserted.

The wizard that generates the DCM core does not support enabling of the DIFF\_TERM attribute of the differential global clock input buffer (IBUFGDS). Therefore the clock input buffer is disabled in the wizard and instead the input buffer is instantiated in the BusyBox top-level wrapper files where the DIFF\_TERM attribute is enabled. This is essential for the design to operate reliable, otherwise the DCM may not lock on the incoming reference clock and the internal clock signals will be full of glitches and spurious behavior.

NOTE: The differential termination could/can also be enabled by constraints in the User Constraints File (UCF).

Figure 5-4: Entity for digital\_clock\_manager

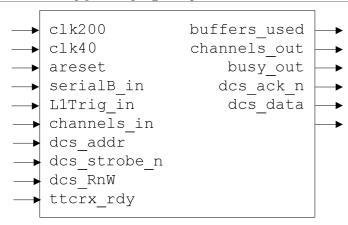

#### 5.4 Busylogic\_top Module

The busylogic\_top module is the common top level for all three firmware versions. It has a structural architecture where all main modules are instantiated and connected.

# **5.4.1** Entity for busylogic\_top Module

Figure 5-5: Entity for BusyBox top module.

| Port Name    | Direction | # Bit | Description                             |

|--------------|-----------|-------|-----------------------------------------|

| clk200       | Input     | 1     | std_logic;                              |

| clk40        | Input     | 1     | std_logic;                              |

| areset       | Input     | 1     | std_logic;                              |

| serialB_in   | Input     | 1     | std_logic;                              |

| L1Trig_in    | Input     | 1     | std_logic;                              |

| channels_in  | Input     | 120   | std_logic_vector(0 to num_of_channels); |

| dcs_addr     | Input     | 16    | std_logic_vector(15 downto 0);          |

| dcs_strobe_n | Input     | 1     | std_logic;                              |

| dcs_RnW      | Input     | 1     | std_logic;                              |

| ttcrx_rdy    | Input     | 1     | std_logic;                              |

| buffers_used | Output    | 4     | std_logic_vector(3 downto 0);           |

| channels_out | Output    | 120   | std_logic_vector(0 to num_ofchannels);  |

| busy_out     | Output    | 1     | std_logic;                              |

| dcs_ack_n    | Output    | 1     | std_logic;                              |

| dcs_data     | In/Out    | 16    | std_logic_vector(15 downto 0);          |

Table 5-4:I/O details for BusyBox Top Module.

## 5.5 Reset\_logic module

This module implements some simple reset logic to generate proper reset signals to the design. The reset signals will be asserted asynchronously whenever the DCM's locked signal is low. In other words, the design will not activate before the DCM locks on the incoming clock. After the DCM achieves lock it will assert the lock signal. The reset logic implements a shift register that is used to delay a synchronous release of the reset signals.

Reset signals for both clock domains are generated. This is done to let the synthesis tools employ "register duplication" to reduce fanout and routing delay of the resets in both clock domains.

| Generic Name | Туре    | Comment                                                                         |

|--------------|---------|---------------------------------------------------------------------------------|

| g_rst_length | natural | Sets the time in number of clock (clk40) cycles before the resets are released. |

Table 5-5: Tabel of generic parameters for reset\_logic module.

| Port Name | Direction | Туре      | Comment                                        |

|-----------|-----------|-----------|------------------------------------------------|

| clk200    | in        | std_logic | 200 MHz clock input                            |

| clk40     | in        | std_logic | 40 MHz clock input                             |

| clk_lock  | in        | std_logic | acts active low asynchronous reset             |

| rst200    | out       | std_logic | synchronous reset for the 200 MHz clock domain |

| rst40     | out       | std_logic | synchronous reset for the 40 MHz clock domain  |

Table 5-6: IO table for reset\_logic module.

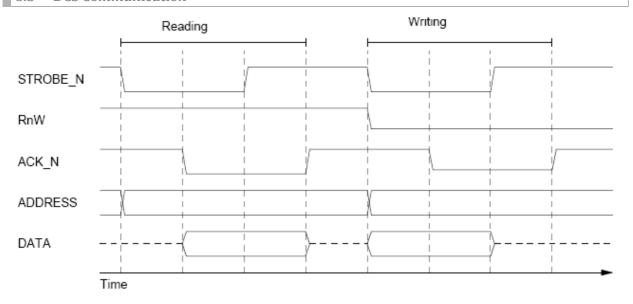

## 5.6 DCS Bus Arbiter and Address Decoder

The DCS bus arbiter and address decoder module is an asynchronous 16 bit data/address handshake protocol for communication between the FPGA and DCS board. This protocol is used to read and write registers in the BusyBox firmware. The MSB of the 16 bits DCS bus address selects which FPGA to communicate with. Then each module can be accessed with the next three bits and the remaining bits are used to target specific sub-module registers.

| FPGA address | Module address | Sub module address |

|--------------|----------------|--------------------|

| 15           | 14 – 12        | 11 – 0             |

Table 5-7: Bit-mapping of DCS bus address.

# 5.6.1 Entity DCS bus arbiter and address decoder

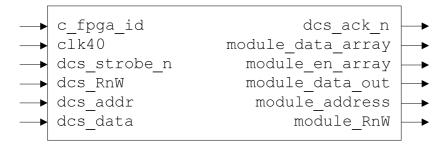

Figure 5-6: Entity for DCS Bus Arbiter and Address Decoder.

| Generic name | Туре      | Comment                                                                   |

|--------------|-----------|---------------------------------------------------------------------------|

| c_fpga_id    | std_logic | This bit sets the slave FPGA MSB address. '0' for FPGA1 or '1' for FPGA2. |

$\textit{Table 5-8: Generic parameters for dcs\_arbit\_addr\_dec}$

| Port Name    | Direction | # Bit | Description                                                                   |

|--------------|-----------|-------|-------------------------------------------------------------------------------|

| clk40        | Input     | 1     | std_logic; the clk40 frequency is 40.08 MHz                                   |

| dcs_strobe_n | Input     | 1     | std_logic; the asynchronous handshake is done with STROBE_N                   |

|              |           |       | from the DCS board.                                                           |

| dcs_RnW      | Input     | 1     | std_logic; '1' read and '0' write.                                            |

| dcs_addr     | Input     | 16    | std_logic_vector(15 downto 0); address module and submodule register.         |

| dcs_data     | Inout     | 16    | std_logic_vector(15 downto 0); bi-directional data line.                      |

| dcs_ack_n    | Output    | 1     | std_logic; the asynchronous handshake is done with ACK_N from the busy board. |

| module_data_array | Output | 7  | std_logic_vector(0 to num_of_modules-1); communication with modules. |

|-------------------|--------|----|----------------------------------------------------------------------|

| module_en_array   | Output | 7  | std_logic_vector(0 to num_of_modules-1); communication with modules. |

| module_address    | Output | 12 | std_logic_vector(11 downto 0); communication with modules.           |

| module_RnW        | Output | 1  | std_logic; communication with modules.                               |

Table 5-9:I/O details for DCS Bus Arbiter and Address Decoder.

#### 5.7 Receiver Module

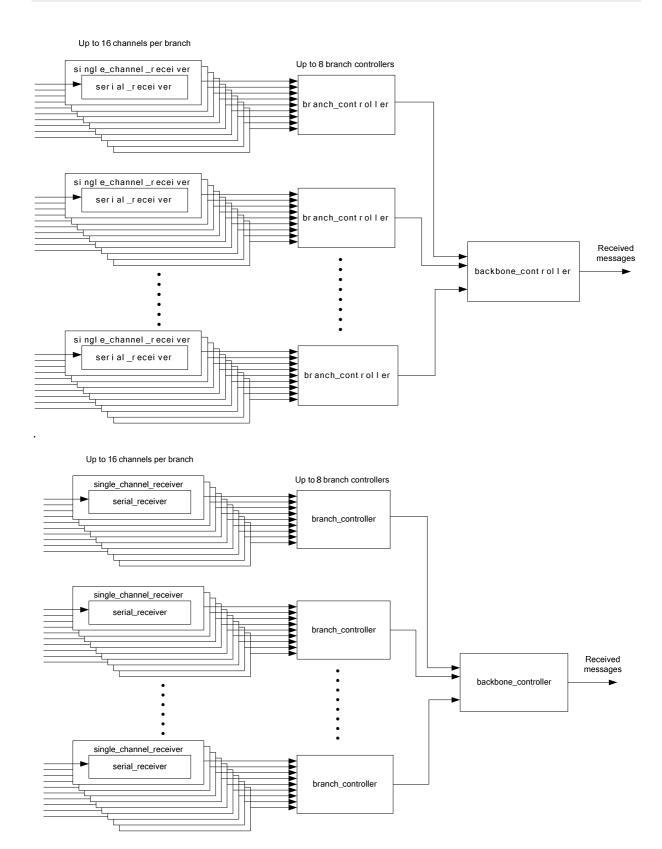

Serial data from the D-RORCs are handled by the receiver module and up to 120 single channels can be implemented in one FPGA.

| Detector | # Channels on FPGA 1 | # Channels on FPGA 2 |

|----------|----------------------|----------------------|

| TPC      | 120                  | 96                   |

| PHOS     | 20                   | N/A                  |

| FMD      | 24                   | N/A                  |

| EMCal    | 3                    | N/A                  |

Table 5-10: Numbers of channels per detector pr FPGA.

In order to implement error tolerance, the 48 bit word from the D-RORC is sampled in a 16 bit data frame. A state machine in the Single Channel Receiver module reads out the data word, one word after another, when the serial decoder flags that data is ready to be sent. A countdown timer in the state machine discards the data if the strict timing between data readout is compromised. In that case the next word is then considered the first in the readout sequence of three words.

If all three words have been read out successfully, and no parity errors and timeouts were found, the state machine will send the data to a multiplexer tree.

Up to sixteen Single Channel Receivers can be connected to a Branch Controller module. The Branch Controller buffers data from the Single Channel Receivers and stops further buffering until data have been read out by the Backbone Controller. The Backbone Controller may have up to eight Branch Controllers and the concept is illustrated in

Figure 5-7: Architecture of multi channel receiver.

# 5.7.1 Receiver Module VHDL Entity Hierarchy

## 1) Multi Channel Receiver

- Single Channel Receiver

- \* Serial Decoder

- Branch Controller

- Backbone Controller

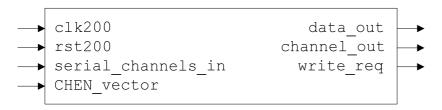

# 5.7.2 Entity Multi Channel Receiver Module

The Multi Channel Receiver module has structural architecture that instantiates and connects the correct numbers of single channel receivers and branch controllers. The single channel serial receivers are connected to branch controllers and the branch controllers are then connected to the backbone controller. See Figure 5-8. The number of channels and number of branches to instantiate is defined through generics.

Figure 5-8: Entity for Channel Receiver Module.

| Port Name         | Direction | # Bit | Description                                                                                                                                    |

|-------------------|-----------|-------|------------------------------------------------------------------------------------------------------------------------------------------------|

| clk200            | Input     | 1     | std_logic; the clk200 frequency is 200 MHz.                                                                                                    |

| areset            | Input     | 1     | std_logic; asynchronous reset                                                                                                                  |

| serial_channel_in | Input     | 120   | <pre>std_logic_vector(0 to num_of_channels); LVDS serial channels from D-RORCs</pre>                                                           |

| CHEN_vector       | Input     | 120   | std_logic_vector(0 to num_of_channels); CHEN vector is a register in the Control and Status Register module , one bit set or disable channels. |

| data_out          | Output    | 48    | std_logic_vector(47 downto 0); 48 bit data from D-RORCs                                                                                        |

| channel_out       | Output    | 8     | std_logic_vector(7 downto 0); toggles the data from the different channels to be outputted                                                     |

| write_req         | Output    | 1     | std_logic; '1' D-RORC data ready to send                                                                                                       |

Table 5-11: I/O details for Channel receiver Module.

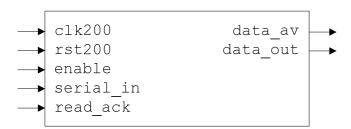

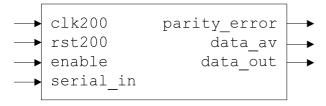

# 5.7.3 Entity Single Channel Receiver

A state machine checks for parity errors and make sure that the 16 bit words from the serial decoder is within the allowed time limit. Three 16 bit words are concatenated to a 48 bit message and stored temporary in three different registers. If the registers are not read out fast enough they will be overwritten.

Figure 5-9: Entity for Single Channel Receiver.

| Port Name | Direction | # Bit | Description                                            |

|-----------|-----------|-------|--------------------------------------------------------|

| clk200    | Input     | 1     | std_logic; the clk200 frequency is 200 MHz.            |

| rst200    | Input     | 1     | std_logic; synchronous rest.                           |

| enable    | Input     | 1     | std_logic;                                             |

| serial_in | Input     | 1     | std_logic; data bit from serial decoder.               |

| data_out  | Output    | 48    | std_logic_vector(47 downto 0); 48 bit data from D-RORC |

| read_ack  | Input     | 1     | std_logic;                                             |

| data_av   | Output    | 1     | std_logic;                                             |

Table 5-12: I/O details for Single Channel Receiver.

## 5.7.4 Entity Serial Decoder

Figure 5-10: Entity for Serial Decoder.

| Port Name    | Direction | # Bit | Description                                     |

|--------------|-----------|-------|-------------------------------------------------|

| clk200       | Input     | 1     | std_logic; the clk200 frequency is 200 MHz.     |

| rst200       | Input     | 1     | std_logic; synchronous reset                    |

| enable       | Input     | 1     | std_logic;                                      |

| serial_in    | Input     | 1     | std_logic; serial signal from D-RORC            |

| parity_error | Output    | 1     | std_logic;                                      |

| data_av      | Output    | 1     | std_logic;                                      |

| data_out     | Output    | 16    | std_logic_vector(15 downto 0); data from D-RORC |

Table 5-13: I/O details for Serial Decoder.

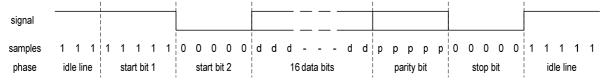

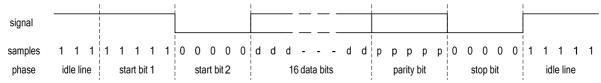

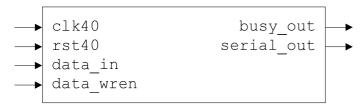

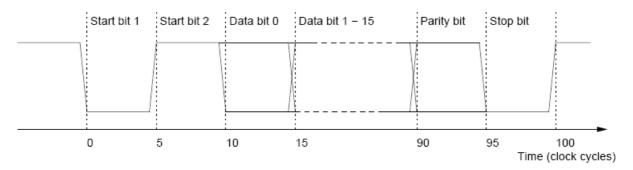

If the Serial Decoder is enabled it listens to the transmission line for serial data. Each data word is packed into a frame and encoded on the serial signal as illustrated in

Figure 5-11. When the line is idle it pulled to logic 1. A frame starts with two start bits to create 1-0 transition. The decoder looks for this transition to lock on to the data frame. Each bit is sampled 5 times. This is necessary to detect the bit phase of the incoming serial bit stream. Once the 1-0 transition of the start bits are found a state machine in the decoder triggers and start capturing data. The state machine picks the sample that is believed to be the middle of each bit by counting samples at the local clock rate. After 16 data bits have been sampled, a parity bit and a stop bit are sampled. Both must have the correct logic value before the frame is accepted and data forwarded. The parity bit is a even parity generated by XOR'ing the data bits as they are received. The stop bit is always logic 0.

Figure 5-11: Encoding of serial data on transmission line.

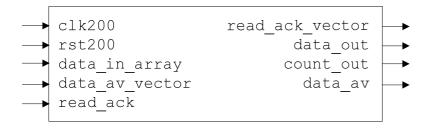

#### 5.7.5 Entity Branch Controller

The Branch Controller reads data from up to 16 Single Channels Receiver's and feed the data to the backbone controller. It scans the receivers for data available flag and copies the data to a buffer when the flag is raised. The branch controller will hold until the Backbone Controller has verified that it has read the message.

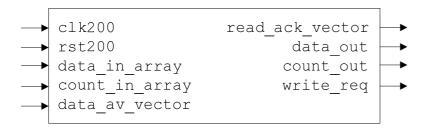

Figure 5-12: Entity for Branch Controller.

| Port Name       | Direction | # Bit | Description                                                       |

|-----------------|-----------|-------|-------------------------------------------------------------------|

| clk200          | Input     | 1     | std_logic; the clk200 frequency is 200 MHz.                       |

| Rst200          | Input     | 1     | std_logic; synchronous reset                                      |

| data_in_array   | Input     | 16    | receiver_busy_array(0 to 15);                                     |

| data_av_vector  | Input     | 16    | std_logic_vector(0 to 15); '1' when data is available             |

| read_ack        | Input     | 1     | std_logic; from backbone controller                               |

| read_ack_vector | Output    | 16    | std_logic_vector(0 to 15);                                        |

| data_out        | Output    | 48    | std_logic_vector(47 downto 0); 48 bit data                        |

| count_out       | Output    | 4     | std_logic_vector(3 downto 0); counter to keep track of serial     |

|                 |           |       | channel being scanned                                             |

| data_av         | Output    | 1     | std_logic; '1' when data from serial receiver is ready to be sent |

Table 5-14: I/O details for Branch Controller.

## 5.7.6 Entity Backbone Controller

The Backbone Controller reads data from up to 8 Branch Controller's and writes the data to the RX Memory module and the D-RORC inbox buffer in the Event Validator Top module.

Figure 5-13: Entity for Backbone Controller.

| Port Name       | Direction | # Bit | Description                                    |

|-----------------|-----------|-------|------------------------------------------------|

| clk200          | Input     | 1     | std_logic; the clk200 frequency is 200 MHz.    |

| rst200          | Input     | 1     | std_logic; synchronous reset                   |

| data_in_array   | Input     | 8     | receiver_bus_array(0 to 7); work.busylogic_pkg |

| count_in_array  | Input     | 8     | count_array(0 to 7); work.busylogic_pkg        |

| read_ack_vector | Output    | 8     | std_logic_vector(0 to 7);                      |

| data_out        | Output    | 48    | std_logic_vector(47 downto 0); 48 bit data     |

| count_out       | Output    | 8     | std_logic_vector(7 downto 0);                  |

| data_av_vector  | Output    | 8     | std_logic_vector(0 to 7);                      |

| write_req       | Output    | 1     | std_logic;                                     |

Table 5-15: I/O details for Backbone Controller.

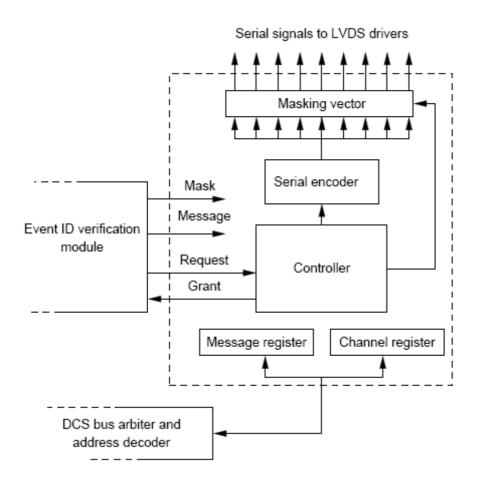

# 5.8 Transmitter Module

The transmitter module transmits serial data to the D-RORCs and consists of a controller, a serial decoder and a masking vector. A message register and a channel register are available for the DCS bus module and Event ID Verification module. Data from the message register will be loaded into the serial encoder and the masking vector will be created based on the channel number in the channel register. The masking vector lets the Event ID Verification module and DCS bus module select which channels to enable or disable. The controller handles requests from the Event ID Verification module and DCS bus module to prevent communication conflicts.

A state machine in the serial encoder module sends a 16 bit word to the PISO (Parallell In –Serial Out) module by request from the controller.

Figure 5-14: Transmitter system. From [Magne]

The transmitter module will request eventIDs from the D-RORCs. The request is a 16 bit word and is sent to all D-RORCs.

| 15 – 12      | 11 – 8     | 7 - 0  |

|--------------|------------|--------|

| Command type | Request ID | Unused |

Table 5-16: Bit map for Trigger module request.

| Request Event ID    | 0100 | Request an Event ID from the D-RORC.                         |

|---------------------|------|--------------------------------------------------------------|

| Resend last message | 0101 | Command the D-RORC to re-transmit the last message sent.     |

| Force pop Event ID  | 0110 | Command the D-RORC to pop one Event ID from its local queue. |

| Force Request ID    | 0111 | Command the D-RORC to store the attached Request ID.         |

Table 5-17: Request commands.

## 5.8.1 Transmitter module VHDL Entity Hierarchy

- Transmitter module

- Serial encoder

The Transmitter module is initiating the serial encoder and setting the masking vector.

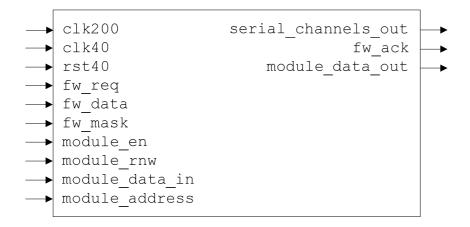

## 5.8.2 Entity Transmitter module

The Transmitter module is initiating the serial encoder and setting the masking vector. A 16 bit register can be accessed from the DCS bus as shown in figure 5-15. The register contains a message register and a channel register.

| temp_dcs_data  |             |  |  |  |  |

|----------------|-------------|--|--|--|--|

| dcs_tx_channel | dcs_tx_data |  |  |  |  |

| 15 – 8         | 7 - 0       |  |  |  |  |

Table 5-18: Bit map for DCS data.

The channel register selects which channel to be masked and unmasked the other channels. If the value in the channels register does not specify a specific channel, all channels are unmasked and the message is broadcasted to all channels. A flag is raised in to indicate that data are available to be written from the DCS board to the message register. A state machine, see figure 5-16, in the controller sees the flag and starts loading data into the serial encoder and sets the masking vector. The flag is removed and the procedure is executed.

The Event ID module sends a request to the transmitter module and the request is granted if there is no pending flag from the DCS bus. The controller loads data and the masking vector from the EventID module.

Messages are Hamming coded in the Transmitter module in an 8:4 code applied to the 4 bit command word and request ID. The receiver (D-RORC) will discard data if it finds any errors. The Hamming function is in the busylogic\_pkg.

| Bit      | 8  | 7  | 6  | 5  | 4  |    | 2  | 1  |

|----------|----|----|----|----|----|----|----|----|

| position | P4 | D4 | D3 | D2 | P3 | D1 | P2 | P1 |

| P1       |    | Χ  |    | X  |    | X  |    | P1 |

| P2       |    | Χ  | X  |    |    | X  | P2 |    |

| P3       |    | Χ  | X  | X  | Р3 |    |    |    |

| P4       | P4 | X  | X  | X  | X  | X  | X  | X  |

Table 5-19: Hamming code table

Figure 5-17: State diagram for TX controller

Figure 5-18: Entity for Transmitter Module.

| Port Name           | Direction | # Bit | Description                                                   |

|---------------------|-----------|-------|---------------------------------------------------------------|

| rst40               | Input     | 1     | std_logic; synchronous reset                                  |

| clk200              | Input     | 1     | std_logic; the clk200 frequency is 200 MHz                    |

| clk40               | Input     | 1     | std_logic; the clk40 frequency is 40.08 MHz                   |

| fw_req              | Input     | 1     | std_logic;                                                    |

| fw_data             | Input     | 8     | std_logic_vector(7 downto 0);                                 |

| fw_mask             | Input     | 120   | std_logic_vector(0 to num_of_channels);                       |

| module_en           | Input     | 1     | std_logic;                                                    |

| module_rnw          | Input     | 1     | std_logic;                                                    |

| module_data_in      | Input     | 16    | std_logic_vector(15 downto 0);                                |

| module_address      | Input     | 12    | std_logic_vector(11 downto 0);                                |

| serial_channels_out | Output    | 120   | std_logic_vector(0 to num_of_channels);                       |

| fw_ack              | Output    | 1     | std_logic;                                                    |

| module_data_out     | Output    | 16    | std_logic_vector(15 downto 0); 16 bit request data to D-RORCs |

Table 5-20: I/O details for Transmitter Module.

## 5.8.3 Entity Serial Encoder

Figure 5-19: Entity for Serial Encoder.

| Port Name  | Direction | # Bit | Description                                    |

|------------|-----------|-------|------------------------------------------------|

| rst40      | Input     | 1     | std_logic; synchronous reset                   |

| clk40      | Input     | 1     | std_logic; ; the clock_in frequency is 200 MHz |

| data_in    | Input     | 1     | std_logic_vector;                              |

| data_wren  | Input     | 1     | std_logic;                                     |

| busy_out   | Output    | 1     | std_logic;                                     |

| serial_out | Output    | 1     | std_logic;                                     |

Table 5-21: I/O details for Serial Encoder.

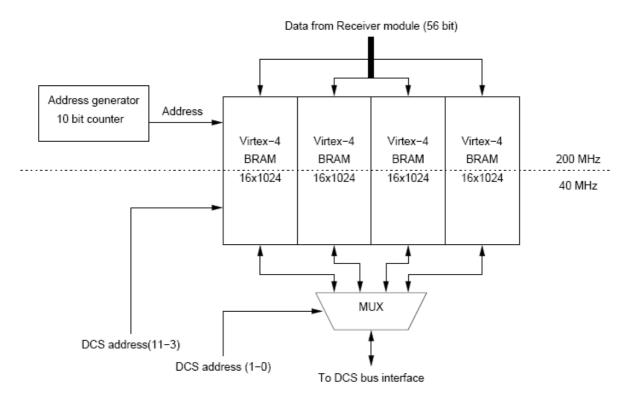

## 5.9 RX Memory Module

The BusyBox can store up to 1024 D-RORC messages from the Receiver module in the RX Memory module. Four BRAM modules are instantiated in the FPGA and can be accessed from both clock domains<sup>4</sup>. Data from the Receiver module is 56 bit and is written into memory at the address given by a 10 bit counter. The DCS bus is limited to read 16 bit at a time, and needs four read operations to get the whole word from memory. The RX Memory module can be written to by the DCS bus for testing and verification purposes.

<sup>&</sup>lt;sup>4</sup> The Receiver module operates in the 200 MHz domain while the internal logic of the BusyBox runs in the 40 MHz domain.

Figure 5-20: Illustration of the RX Memory module. From [Magne].

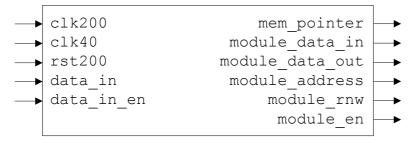

# 5.9.1 Entity RX Memory Module

Figure 5-21: Entity for RX Memory Module.

| Port Name       | Direction | # Bit | Description                                 |

|-----------------|-----------|-------|---------------------------------------------|

| clk200          | Input     | 1     | std_logic; the clk200 frequency is 200 MHz  |

| clk40           | Input     | 1     | std_logic; the clk40 frequency is 40.08 MHz |

| rst200          | Input     | 1     | std_logic; synchronous reset                |

| rst40           | Input     | 1     | std_logic; synchronous reset                |

| data_in         | Input     | 64    | std_logic_vector(63 downto 0);              |

| data_in_en      | Input     | 1     | std_logic;                                  |

| mem_pointer     | Output    | 10    | std_logic_vector(9 downto 0);               |

| module_data_in  | Output    | 16    | std_logic_vector(15 downto 0);              |

| module_data_out | Output    | 16    | std_logic_vector(15 downto 0);              |

| module_address  | Output    | 12    | std_logic_vector(11 downto 0);              |

| module_rnw      | Output    | 1     | std_logic;                                  |

| module_en       | Output    | 1     | std_logic;                                  |

Table 5-22: I/O details for RX Memory Module.

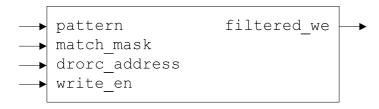

## 5.10 RX Memory Filter Module

The RX Memory filter can be used to filter which messages from specific channels will trigger the write enable signal form the RX Memory Module. Each message from the Receiver Module will have an 8 bit channel number appended to it. Each individual bit of this 8 bit word can be compared with bits in a register in the RX Memory Filter that is accessible from the DCS bus interface. The RX Memory Filter has registers with 16 bits. The first 8 bits are used to toggle matching individual bits. The last 8 bits are the bits that will be compared with the channel number bits of the message. This feature makes it easier to see the response of only a subset of channels in the RX Memory without disabling the other channels in the CHEN registers.

#### 5.10.1 Entity RX Memory Filter Module

Figure 5-22: Entity for RX Memory Filter.

| Port Name     | Direction | # Bit | Description                   |

|---------------|-----------|-------|-------------------------------|

| pattern       | Input     | 8     | std_logic_vector(7 downto 0); |

| match_mask    | Input     | 8     | std_logic_vector(7 downto 0); |

| drorc_address | Input     | 8     | std_logic_vector(7 downto 0); |

| write_en      | Input     | 1     | std_logic;                    |

| filtered_we   | Output    | 1     | std_logic;                    |

Table 5-23: I/O details for RX Memory Filter.

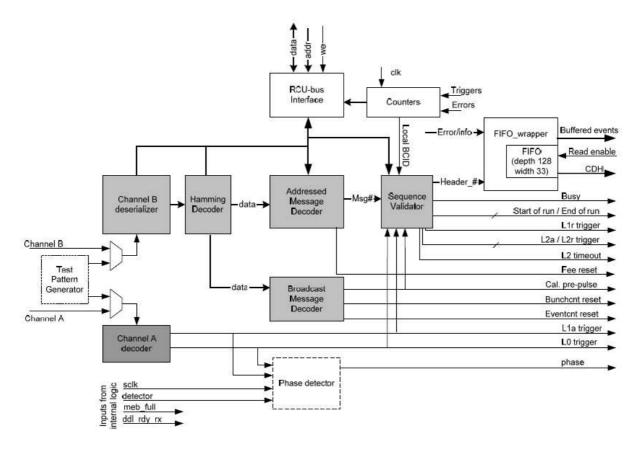

## 5.11 Trigger Receiver Module

The optical signals from the CTP are converted to electrical signals by the TTCrx chip on the DCS board into Channel A and Channel B. The Trigger Receiver module decodes the information and stores it in a FIFO in the CDH (Common Data Header) format. Triggers will appear as individual signal at the module outputs.

Channel A transmits the LO and L1 triggers. Channel B transmits the broadcast message and the individually addressed messages. The addressed messages are decoded into the CDH format and put in a FIFO. The BusyBox extracts the event ID (OrbitID + BunchCountID), event info and event errors from the CDH. Figure 5-23 shows an overview of the Trigger Receiver module.

Figure 5-24: Block diagram of the Trigger Receiver module. From [Johan].

# 5.11.1 Entity Trigger Receiver Module

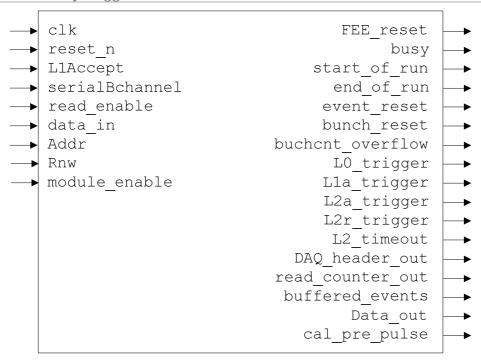

Figure 5-25: Entity for Trigger Receiver Module.

| Port Name         | Direction | # Bit | Description                               |

|-------------------|-----------|-------|-------------------------------------------|

| clk               | Input     | 1     | std_logic; the clk frequency is 40.08 MHz |

| reset_n           | Input     | 1     | std_logic;                                |

| L1Accept          | Input     | 1     | std_logic;                                |

| serialBchannel    | Input     | 1     | std_logic;                                |

| read_enable       | Input     | 1     | std_logic;                                |

| data_in           | Input     | 16    | std_logic_vector(15 downto 0);            |

| addr              | Input     | 12    | std_logic_vector(11 downto 0);            |

| rnw               | Input     | 1     | std_logic;                                |

| module_enable     | Input     | 1     | std_logic;                                |

| FEE_reset         | Output    | 1     | std_logic; N/A                            |

| busy              | Output    | 1     | std_logic;                                |

| cal_pre_pulse     | Output    | 1     | std_logic; N/A                            |

| start_of_run      | Output    | 1     | std_logic; N/A                            |

| end_of_run        | Output    | 1     | std_logic; N/A                            |

| event_reset       | Output    | 1     | std_logic; N/A                            |

| bunch_reset       | Output    | 1     | std_logic; N/A                            |

| bunchcnt_overflow | Output    | 1     | std_logic; N/A                            |

| L0_trigger        | Output    | 1     | std_logic;                                |

| L1a_trigger       | Output    | 1     | std_logic;                                |

| L2a_trigger       | Output    | 1     | std_logic;                                |

| L2r_trigger       | Output    | 1     | std_logic;                                |

| L2_timeout        | Output    | 1     | std_logic;                                |

| DAQ_header_out    | Output    | 33    | std_logic_vector(32 downto 0);            |

| read_counter_out  | Output    | 4     | std_logic_vector(3 downto 0);             |

| buffered_events   | Output    | 4     | std_logic_vector(3 downto 0);             |

| data_out          | Output    | 16    | std_logic_vector(15 downto 0);            |

Table 5-24: I/O details for Trigger Receiver Module.

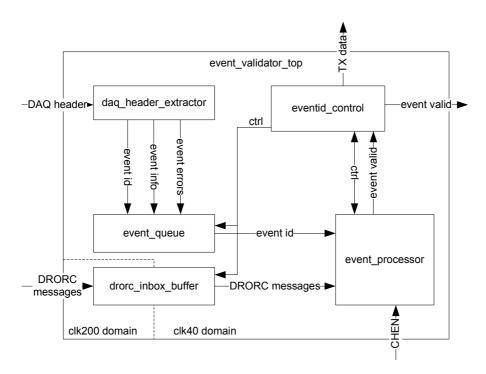

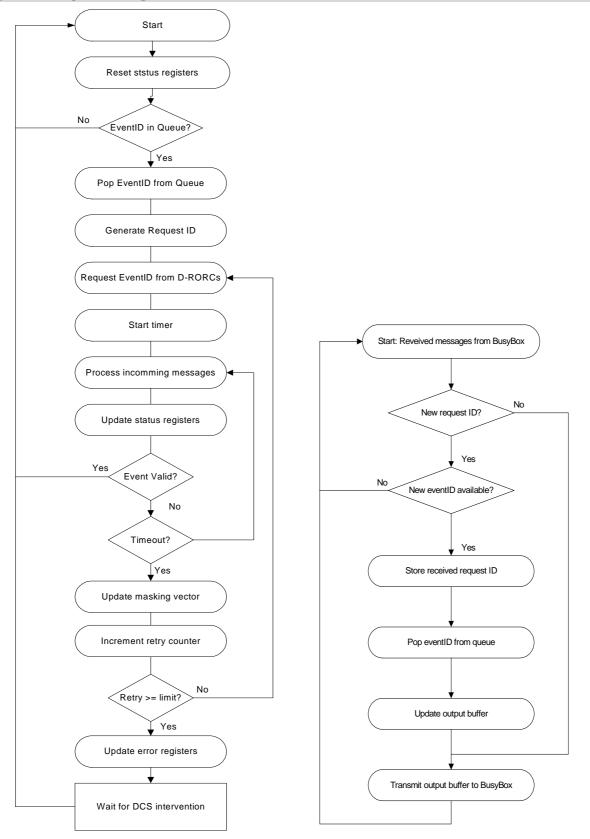

#### 5.12 Event ID Verification Module

The Trigger Receiver module's FIFO is constantly monitored by the Event ID Verification module. Data from an L2a/L2r or L2 timeout trigger is stored in the CDH format in the FIFO and will be read out by the Event ID Queue module.

The event controller then requests the Transmitter module to read out the data and send it to the D-RORCs. The Receiver module forwards D-RORC data to the D-RORC Inbox Buffer. The Inbox operates in both frequency domains  $^5$  and makes the data available for the Event processor, which compares the event ID.

The Event Processor has a register called EIDOK (Event ID OK), and together with the CHEN vector it compares the two event IDs from the Event ID Queue module and the D-RORC Inbox buffer. If the ID matches, the verification gate will assert an event verified signal. An overview of the ID verification model is shown in The BusyBox has no direct communication with the FEE and keeps track of available buffers by communicating with the D-RORCs. The Trigger System sends triggers to the BusyBox and the FEE. Figure 3-1

Figure 5-26: Illustration of the structure of event\_validator\_top module.

The eventid\_control block controls the flow of new eventIDs from the event\_queue and DRORC messages from the drorc\_inbox\_buffer to the event\_processor. It is also commands the TX controller to transmit requests to the DRORCs. The event\_processor block determines when the current event has been verified/validated.

## 5.12.1 Event\_validator\_top VHDL Entity Hierarchy

- Event\_validator\_top

- i\_daq\_header\_extractor: daq\_header\_extractor

- i\_event\_queue: FIFOsync108x512(Core)

- o i\_eventid\_control: eventid\_control

- o i\_event\_processor : event\_processor

<sup>&</sup>lt;sup>5</sup> The Receiver module operates in the 200 MHz domain while the internal logic of the verification module runs in the 40 MHz domain.

## i\_drorc\_inbox\_buffer: drorc\_inbox\_buffer (Core)

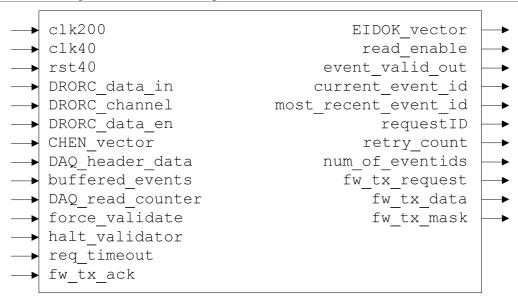

# 5.12.2 Entity Event\_validator\_top

Figure 5-27: Entity for event\_validator\_top module.

| Port Name            | Direction | # Bit | Description                                 |

|----------------------|-----------|-------|---------------------------------------------|

| rst40                | Input     | 1     | std_logic; synchronous reset                |

| clk200               | Input     | 1     | std_logic; the clk200 frequency is 200 MHz  |

| clk40                | Input     | 1     | std_logic; the clk40 frequency is 40.08 MHz |

| DRORC_data_in        | Input     | 48    | std_logic_vector(47 downto 0);              |

| DRORC_channel        | Input     | 8     | std_logic_vector(7 downto 0);               |

| DRORC_data_en        | Input     | 1     | std_logic;                                  |

| CHEN_vector          | Input     | 120   | std_logic_vector(0 to num_of_channels);     |

| DAQ_header_data      | Input     | 33    | std_logic_vector(32 downto 0);              |

| buffered_events      | Input     | 4     | std_logic_vector(3 downto 0);               |

| DAQ_read_counter     | Input     | 4     | std_logic_vector(3 downto 0);               |

| force_validate       | Input     | 1     | std_logic;                                  |

| halt_validator       | Input     | 1     | std_logic;                                  |

| req_timeout          | Input     | 16    | std_logic_vector(15 downto 0);              |

| fw_tx_ack            | Input     | 1     | std_logic;                                  |

| EIDOK_vector         | Output    | 120   | std_logic_vector(0 to num_of_channels);     |

| read_enable          | Output    | 1     | std_logic;                                  |

| event_valid_out      | Output    | 1     | std_logic;                                  |

| current_event_id     | Output    | 36    | std_logic_vector(35 downto 0);              |

| most_recent_event_id | Output    | 36    | std_logic_vector(35 downto 0);              |

| requestID            | Output    | 4     | std_logic_vector(3 downto 0);               |

| retry_count          | Output    | 16    | std_logic_vector(15 downto 0);              |

| num_of_eventids      | Output    | 4     | std_logic_vector(3 downto);                 |

| fw_tx_request        | Output    | 1     | std_logic;                                  |

| fw_tx_data           | Output    | 8     | std_logic_vector(7 downto 0);               |

| fw_tx_mask           | Output    | 120   | std_logic_vector(0 to num_of_channels);     |

Table 5-25: I/O details for Event Validator.

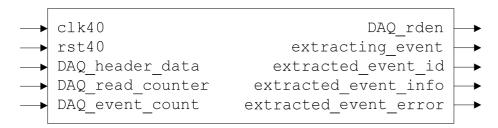

# 5.12.3 Entity DAQ Header Extractor

This module reads out the DAQ header (also called CDH (Common Data Header)) that the trigger receiver module generates and buffers. The Trigger Receiver Module stores the DAQ header as 9 32 bit words in an internal FIFO. Each word contains information about the received trigger sequence. The DAQ Header Extractor reads out all 9 words and outputs selected fields of information in parallel. Most importantly the EventID is extracted from the header. The extracted information is to a FIFO. The information is also forwarded to the Control and Status Register module.

Figure 5-28: Entity for EventID Extractor.

| Port Name             | Direction | # Bit | Description                                                                 |

|-----------------------|-----------|-------|-----------------------------------------------------------------------------|

| clk40                 | Input     | 1     | std_logic; the clock_in frequency is 40.08 MHz                              |

| rst40                 | Input     | 1     | std_logic; synchronous reset                                                |

| DAQ_header_data       | Input     | 33    | std_logic_vector(32 downto 0); 33 bit word                                  |

| DAQ_read_counter      | Input     | 4     | std_logic_vector(3 downto 0); counts through the 9 words in the CDH message |

| DAQ_event_count       | Input     | 4     | std_logic_vector(3 downto 0); counts numbers of buffered events in the FIFO |

| DAQ_rden              | Output    | 1     | std_logic;                                                                  |

| extracting_event      | Output    | 1     | std_logic; status output                                                    |

| extracted_event_id    | Output    | 36    | std_logic_vector(35 downto 0); the extracted orbit end bunch cross IDs      |

| extracted_event_info  | Output    | 13    | std_logic_vector(12 downto 0);                                              |

| extracted_event_error | Output    | 25    | std_logic_vector(                                                           |

|                       |           |       |                                                                             |

Table 5-26: I/O details for EventID Extractor.

## 5.12.4 Entity EventID Control

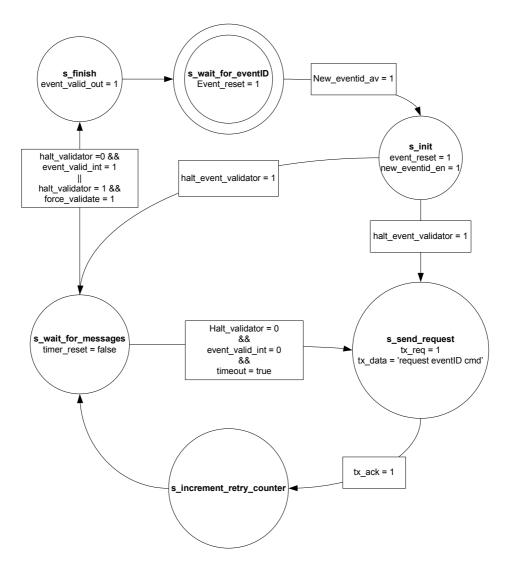

The EventID Control module is a state machine that monitors and controls the event verification process. Under is a state diagram of the controller.

Figure 5-29: State diagram for EventID Controller.

Figure 5-30: Entity for EventID Control.

| Port Name       | Direction | # Bit | Description                                 |

|-----------------|-----------|-------|---------------------------------------------|

| clk40           | Input     | 1     | std_logic; the clk40 frequency is 40.08 MHz |

| rst40           | Input     | 1     | std_logic; synchronous reset                |

| force_validate  | Input     | 1     | std_logic;                                  |

| halt_validator  | Input     | 1     | std_logic;                                  |

| new_eventid_av  | Input     | 1     | std_logic;                                  |

| inbox_emty      | Input     | 1     | std_logic;                                  |

| event_valid_int | Input     | 1     | std_logic;                                  |

| req_timeout     | Input     | 16    | std_logic_vector(15 downto 0);              |

| tx_ack          | Input     | 1     | std_logic;                                  |

| new_evetid_en   | Output    | 1     | std_logic;                                  |

| inbox_read_req  | Output    | 1     | std_logic;                                  |

| event_valid_out | Output    | 1     | std_logic;                                  |

| event_reset     | Output    | 1     | std_logic;                                  |

| tx_req          | Output    | 1     | std_logic;                                  |

| tx_data         | Output    | 8     | std_logic_vector(7 downto 0);               |

| requestID       | Output    | 4     | std_logic_vector(3 downto 0);               |

| retry_count     | Output    | 16    | std_logic_vector(15 downto 0);              |

Table 5-27: I/O details for EventID Control.

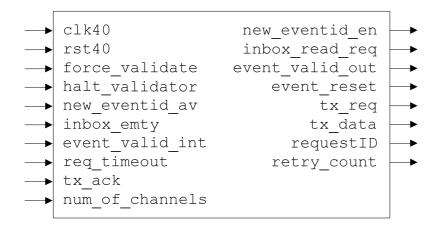

## 5.12.5 Entity EventID Processor

In this module all the verification occurs and based on the CEHN register it will continuously compare the event IDs and set each individual channel with '1' if match or '0' if mismatch in a register called EIDOK. A verification gate will flag an event verified signal if either the CHEN register is disabled or all channels where checked in the EIDOK register.

Figure 5-31: Entity for EventID Processor.

| Port Name       | Direction | # Bit | Description                                 |

|-----------------|-----------|-------|---------------------------------------------|

| clk40           | Input     | 1     | std_logic; the clk40 frequency is 40.08 MHz |

| rst40           | Input     | 1     | std_logic; synchronous reset                |

| trigger_eventid | Input     | 36    | std_logic_vector(35 downto 0);              |

| DRORC-message   | Input     | 56    | std_logic_vector(55 downto 0);              |

| CHEN_vector     | Input     | 120   | std_logic_vector(0 to num_of_channels);     |

| local_requestID | Input     | 4     | std_logic_vector(3 downto 0);               |

| event_reset     | Input     | 1     | std_logic;                                  |

| EIDOK_vector    | Output    | 120   | std_logic_vector(0 to num_of_channels);     |

| tx_mask         | Output    | 120   | std_logic_vector(0 to num_of_channels);     |

| event_valid     | Output    | 1     | std_logic;                                  |

Table 5-28: I/O details for EventID Processor.

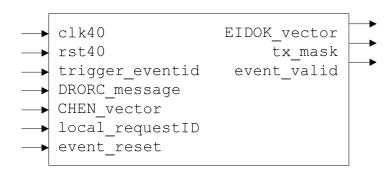

## 5.13 Busy Controller Module

The busy\_controller module is responsible for generating the BUSY signal. It does this by evaluating inputs from other modules and counting occupied Multi Event Buffers (MEB) in the FEE.

There are four conditions that sets the busy signal high and only one have to be true:

Figure 5-32: BUSY generation.

- 1. The TTCrx ready (ttcrx\_rdy) is added to the BusyBox since each sub-detector should report busy if this is not asserted. If there is a physical problem with the connection to the LTU or the CTP is issuing a global reset, the busy is set [JohanA]. Every time a L0 trigger is detected a countdown timer (timeout\_active) starts and the busy is set for this time period. The busy time can be set manually with a register in the Control and Status Register module.

- 2. The busy\_controller keeps track of how many Multi Event Buffers (MEB) are occupied in the FEE. If the number of occupied MEBs is greater or equal than then a programmable limit then BUSY is asserted.

- 3. The BUSY is asserted whenever the trigger receiver is busy, which means we are in the middle of a trigger sequence.

- 4. The Busy Controller module increment a register (buffer\_count) when a L0 is detected (L1 for TPC), decrements the register when a L2 Reject trigger is asserted and when the Event ID Verification module asserts the event valid signal.

The number of occupied MEBs is calculated by monitoring the triggers and the validation of event IDs process.

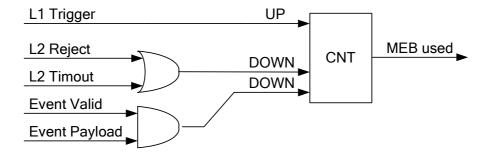

Figure 5-33: MEB counter.

The counter is incremented when a L1 trigger is seen. It decrements on a L2 Reject or L2 Timeout and when event valid and event payload is active at the same time. See Figure 5-33.

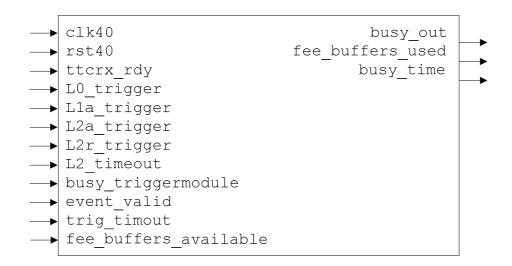

#### **5.13.1** Entity Busy Controller Module

Figure 5-34: Entity for Busy Controller Module.

| Port Name             | Direction | # Bit | Description                                                                                                                                                                                                            |

|-----------------------|-----------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| rst40                 | Input     | 1     | std_logic; synchronous resets                                                                                                                                                                                          |

| clk40                 | Input     | 1     | std_logic; the clk40 frequency is 40.08 MHz.                                                                                                                                                                           |

| ttcrx_rdy             | Input     | 1     | std_logic; ttcrx_rdy out from dcs_ctrl7 (physical line on the DCS-RCU connector). If not asserted it implies a physical problem with connection to the LTU, or that the CTP is issuing a global reset via the TTCrx.   |

| L0_trigger            | Input     | 1     | std_logic; N/A                                                                                                                                                                                                         |

| L1a_trigger           | Input     | 1     | std_logic; L1a_trigger output from trigger_receiver_busy_model. Starts buffering data in Fee if L1a_trigger signal is asserted.                                                                                        |

| L2a_trigger           | Input     | 1     | std_logic; N/A                                                                                                                                                                                                         |

| L2r_trigger           | Input     | 1     | std_logic; L1r_trigger output from trigger_receiver_busy_model. Overwrites buffers in Fee if L2r_trigger signal is asserted.                                                                                           |

| L2_timeout            | Input     | 1     | std_logic; L2_timeout output from trigger_receiver_busy_model. Overwrites buffers in Fee if L2_timeout signal is asserted.                                                                                             |

| busy_triggermodule    | Input     | 1     | std_logic; busy_triggermodule output from trigger_receiver_module.                                                                                                                                                     |

| event_valid           | Input     | 1     | std_logic;                                                                                                                                                                                                             |

| trig_timeout          | Input     | 16    | std_logic_vector(15 downto 0); programmable timeout following the start of a trigger sequence. 10 us resolution. Register 0x2008 in Control and Status Register. Set Register to A (10 decimal) to get 100 us timeout. |

| fee_buffers_available | Input     | 4     | std_logic_vector(3 downto 0); Holds the numbers of buffers assumed on the FEE. Register 0x2009. Default is 4.                                                                                                          |

| busy_out              | Output    | 1     | std_logic; busy_out is asserted when busy conditions are met.                                                                                                                                                          |

| fee_buffers_used      | Output    | 4     | std_logic_vector(3 downto 0);                                                                                                                                                                                          |

| busy_time             | Output    | 32    | std_logic_vector(31 downto 0); busy_time count numbers of clock cycles busy signal is asserted.                                                                                                                        |

Table 5-29: I/O details for Busy Controller Module.

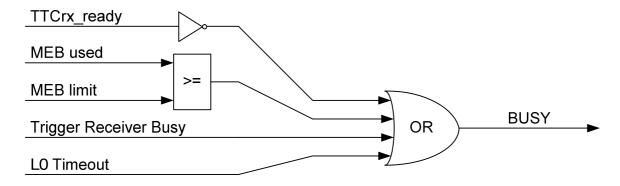

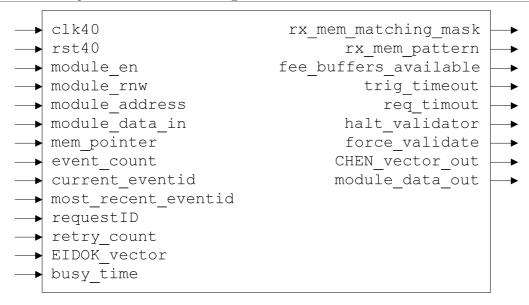

# 5.14 Control and Status Registers

This module has information about register and control signals available for the BusyBox. See chapter 8 for more information.

# 5.14.1 Entity Control and Status Register

Figure 5-35: Entity for Control and Status Registers.

| Port Name             | Direction | # Bit | Description                                 |

|-----------------------|-----------|-------|---------------------------------------------|

| clk40                 | Input     | 1     | std_logic; the clk40 frequency is 40.08 MHz |

| rst40                 | Input     | 1     | std_logic; synchronous resets               |

| module_en             | Input     | 1     | std_logic;                                  |

| module_rnw            | Input     | 1     | std_logic;                                  |

| module_address        | Input     | 12    | std_logic_vector(11 downto 0);              |

| module_data_in        | Input     | 16    | std_logic_vector(15 downto 0);              |

| mem_pointer           | Input     | 10    | std_logic_vector(9 downto 0);               |

| event_count           | Input     | 4     | std_logic_vector(3 downto 0);               |

| current_eventid       | Input     | 36    | std_logic_vector(35 downto 0);              |

| most_recent_eventid   | Input     | 36    | std_logic_vector(35 downto 0);              |

| requestID             | Input     | 4     | std_logic_vector(3 downto 0);               |

| retry_count           | Input     | 16    | std_logic_vector(15 downto 0);              |

| EIDOK_vector          | Input     | 120   | std_logic_vector(0 to num_of_channels);     |

| busy_time             | Input     | 32    | std_logic_vector(31 downto 0);              |

| module_data_out       | Output    | 16    | std_logic_vector(15 downto 0);              |

| rx_mem_matching_mask  | Output    | 8     | std_logic_vector(7 downto 0);               |

| rx_mem_pattern        | Output    | 8     | std_logic_vector(7 downto 0);               |

| fee_buffers_available | Output    | 4     | std_logic_vector(3 downto 0);               |

| trig_timeout          | Output    | 16    | std_logic_vector(15 downto 0);              |

| req_timout            | Output    | 16    | std_logic_vector(15 downto 0);              |

| halt_validator        | Output    | 1     | std_logic;                                  |

| force_validate        | Output    | 1     | std_logic;                                  |

| CHEN_vector_out       | Output    | 120   | std_logic_vector(0 to num_of_channels);     |

Table 5-30: I/O details for Control and Status Registers.

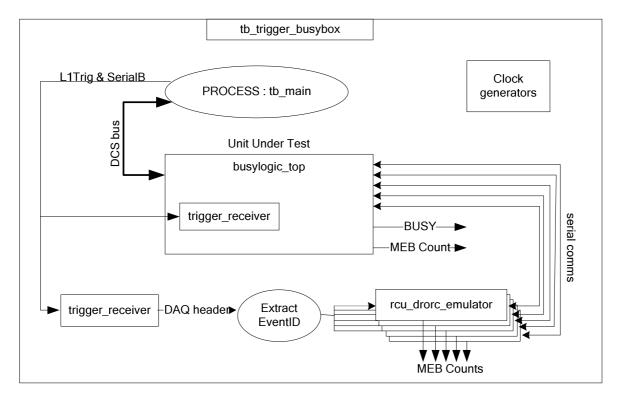

# 6 Functional verification of the BusyBox firmware

## 6.1 Introduction

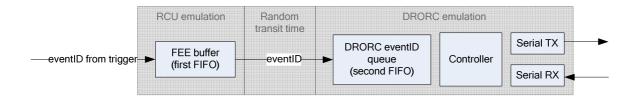

This chapter describes a testbench for the BusyBox firmware. The testbench is designed to emulate a complete environment around the BusyBox top level module busylogic\_top. The FPGA specific wrappers are not included in the test setup.

The BusyBox interacts with the outside world through numerous interfaces:

- 1. Clocks & Reset

- 2. Trigger System; L1Trig and SerialB

- 3. DCS bus

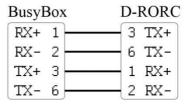

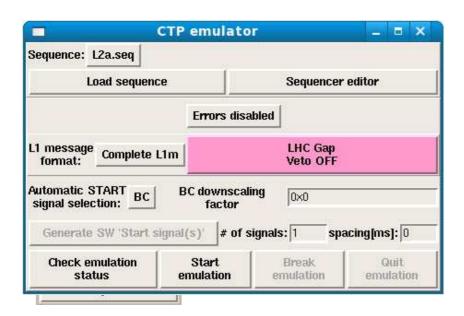

- 4. Serial RX and TX to DRORCs